Pin description – Rainbow Electronics MAX11008 User Manual

Page 13

MAX11008

Dual RF LDMOS Bias Controller with

Nonvolatile Memory

______________________________________________________________________________________

13

______________________________________________________________________________________

13

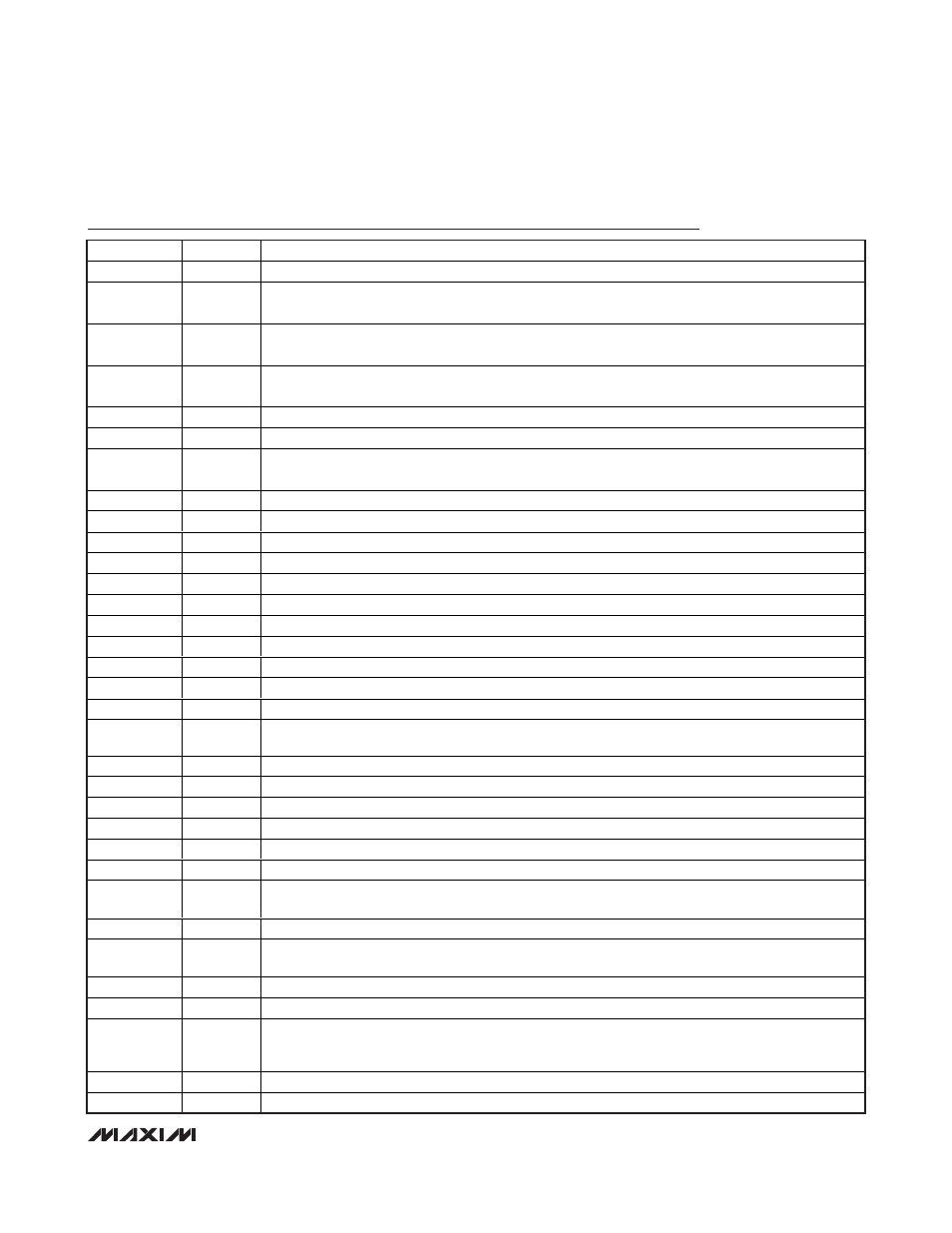

Pin Description

PIN

NAME

FUNCTION

1, 31

DGND

Digital Ground. Connect both DGND inputs to the same potential.

2

OPSAFE1

Output Safe Switch Logic Input 1. Drive OPSAFE1 high to close the output safe switch and clamp

GATE1 to AGND. Drive OPSAFE1 low to open the switch.

3

A0/

CS

Address-Select Input 0/Chip-Select Input. In I

2

C mode, this is the address-select input 0. See Table

1. In SPI mode, this is the chip-select input.

4

CNVST

Active-Low Conversion Start Input. Drive

CNVST low to begin a conversion when in clock modes 01

and 11.

5

SPI/

I2C

Interface-Select Input. Connect to DGND for I

2

C interface. Connect to DV

DD

for SPI interface.

6

ALARM

Alarm Output

7

OPSAFE2

Output Safe Switch Logic Input 2. Drive OPSAFE2 high to close the output safe switch and clamp

GATE2 to AGND. Drive OPSAFE2 low to open the switch.

8

REFDAC

DAC Reference Input/Output

9

REFADC

ADC Reference Input/Output

10

DXP1

Temperature Diode Positive Input 1. Connect DXP1 to the anode of the external diode.

11

DXN1

Temperature Diode Negative Input 1. Connect DXN1 to the cathode of the external diode.

12

DXP2

Temperature Diode Positive Input 2. Connect DXP2 to the anode of the external diode.

13

DXN2

Temperature Diode Negative Input 2. Connect DXN2 to the cathode of the external diode.

14

ADCIN1

ADC Auxiliary Input 1

15

ADCIN2

ADC Auxiliary Input 2

16

PGAOUT2

Programmable-Gain Amplifier Output 2

17

GATE2

Gate-Drive Amplifier Output 2

18

GATE1

Gate-Drive Amplifier Output 1

19, 25, 30,

34–39, 42, 48

N.C.

No Connection. Not internally connected. Leave unconnected.

20, 24

AV

DD

Analog-Supply Input. Connect both AV

DD

inputs to the same potential.

21, 22, 23

AGND

Analog Ground. Connect all AGND inputs to the same potential.

26

CS2+

C ur r ent- S ense P osi ti ve Inp ut 2. C S 2+ i s the exter nal sense- r esi stor connecti on to the LD M OS 2 sup p l y.

27

CS2-

Current-Sense Negative Input 2. CS2- is the external sense-resistor connection to the LDMOS 2 drain.

28

CS1-

Current-Sense Negative Input 1. CS1- is the external sense-resistor connection to the LDMOS 1 drain.

29

CS1+

C ur r ent- S ense P osi ti ve Inp ut 1. C S 1+ i s the exter nal sense- r esi stor connecti on to the LD M OS 1 sup p l y.

32, 33, 47

DV

DD

Digital-Supply Input. Connect all DV

DD

inputs to the same potential. Connect a 0.1µF capacitor to

DV

DD

.

40

PGAOUT1

Programmable-Gain Amplifier Output 1

41

A2/N.C.

Address-Select Input 2/N.C. In I

2

C mode, this pin is the address-select input 2. See Table 1. In SPI

mode, this is a no connection pin.

43

SCL/SCLK

Serial-Clock Input. SCL is the I

2

C-compatible clock input. SCLK is the SPI-compatible clock input.

44

SDA/DIN

S er i al - D ata Inp ut/Outp ut. S D A i s the I

2

C- com p ati b l e i np ut/outp ut. D IN i s the S P I- com p ati b l e d ata i np ut.

45

A1/DOUT

Address-Select Input 1/Data Out. In I

2

C mode, this is the address-select input 1. See Table 1. In SPI

mode, this is the serial-data output. Data is clocked out on the falling edge of SCLK. DOUT is a high-

impedance output when

CS is driven high.

46

BUSY

Busy Output. BUSY goes high to indicate activity.

—

EP

Exposed Pad. Connect EP to AGND. Internally connected to AGND.