Rf01 – Rainbow Electronics RF01 User Manual

Page 17

RF01

FIFO and clear its content. Bit 0 modifies the function of pin 6 and pin 7. Pin 6 (nFFS) will become input if fe

is set to 1. If the chip is used in FIFO mode, do not allow this to be a floating input.

Reset Mode Command

bit 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 POR

1 1 0 1 1 0 1 0 0 0 0 0 0 0 0 dr DAOOh

Bit 0 (dr): Disables the highly sensitive RESET mode. If this bit is cleared, a 600 mV glitch in the power supply

may cause a system reset. For

more detailed description see the Reset modes section.

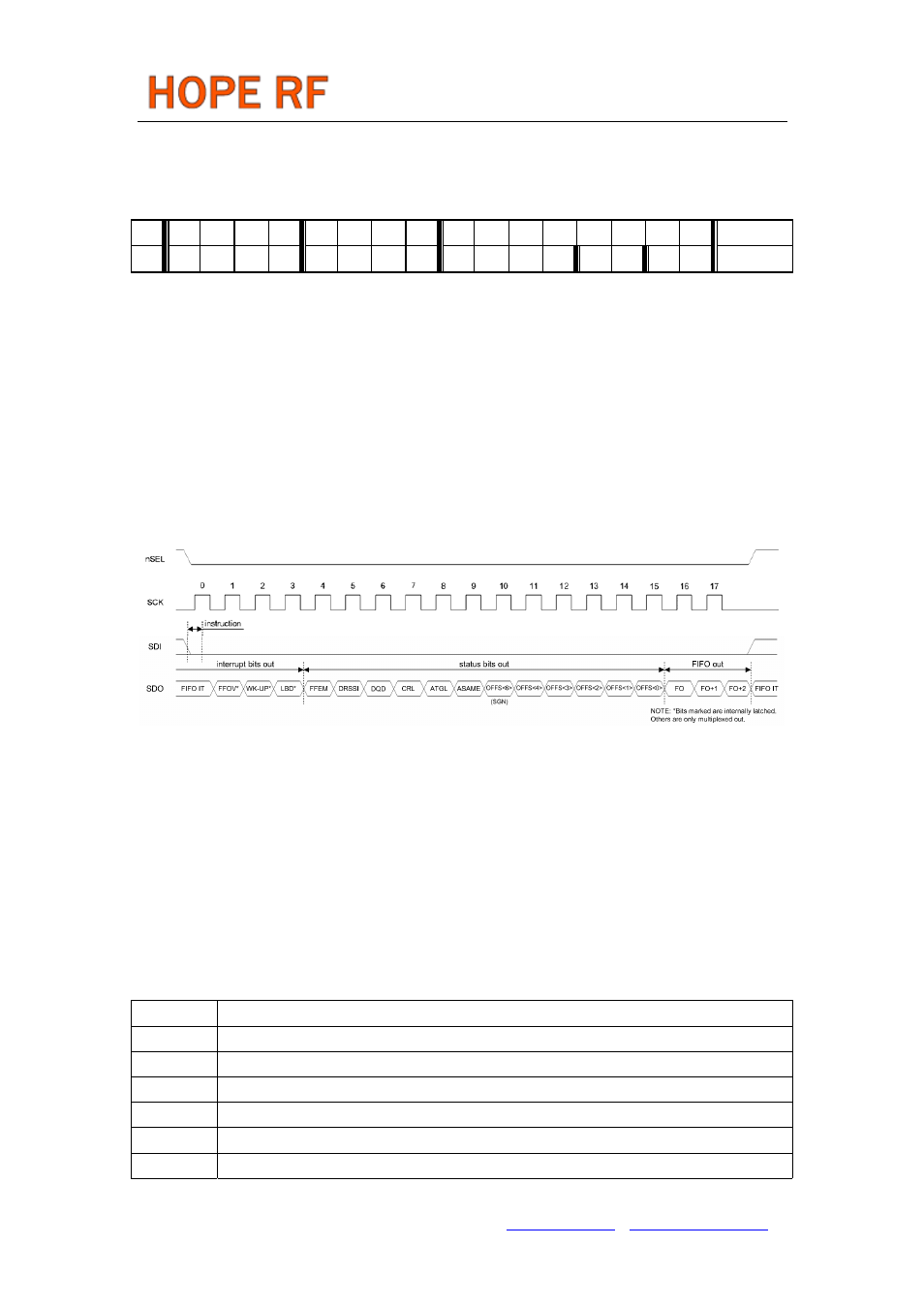

Status Read Command:

The read command starts with a zero, whereas all other control commands start with a one.

Therefore, after receiving the first bit of the control command the RF01 identifies it as a read command.

So as the first bit of the command is received, the receiver starts to clock out the status bits on the SDO

output as follows:

Status Register Read Sequence with FIFO Read Example

It is possible to read out the content of the FIFO after the reading of the status bits. The command can be

aborted after any read bits by rising edge of the select signal.

Note:

The FIFO IT bit behaves like a status bit, but generates nIRQ pulse if active. To check whether there

is a sufficient amount of data in the FIFO, the SDO output can be tested. In extreme speed critical

applications, it can be useful to read only the first four bits (FIFO IT -LBD) to clear the FFOV, WK-UP, and

LBD bits. During the FIFO access the f

SCK

cannot be higher than f

ref

/4, where f

ref

is the crystal oscillator

frequency. If the FIFO is read in this mode the nFFS input must be connected to logic high level.

Definitions of the bits in the above timing diagram:

FIFO IT

Number of the data bits in the FIFO is reached the preprogrammed limit

FFOV

FIFO overflow

WK-UP

Wake-up timer overflow

LBD

Low battery detect, the power supply voltage is below the preprogrammed limit

FFEM

FIFO is empty

DRSSI

The strength of the incoming signal is above the preprogrammed limit

DQD

Data Quality Detector detected a good quality signal

Tel: +86-755-86096587 Fax: +86-755-86096602 E-mail: [email protected] http://www.hoperf.com