Rainbow Electronics MAX5961 User Manual

Page 39

MAX5961

0 to 16V, Quad, Hot-Swap Controller

with 10-Bit Current and Voltage Monitor

______________________________________________________________________________________

39

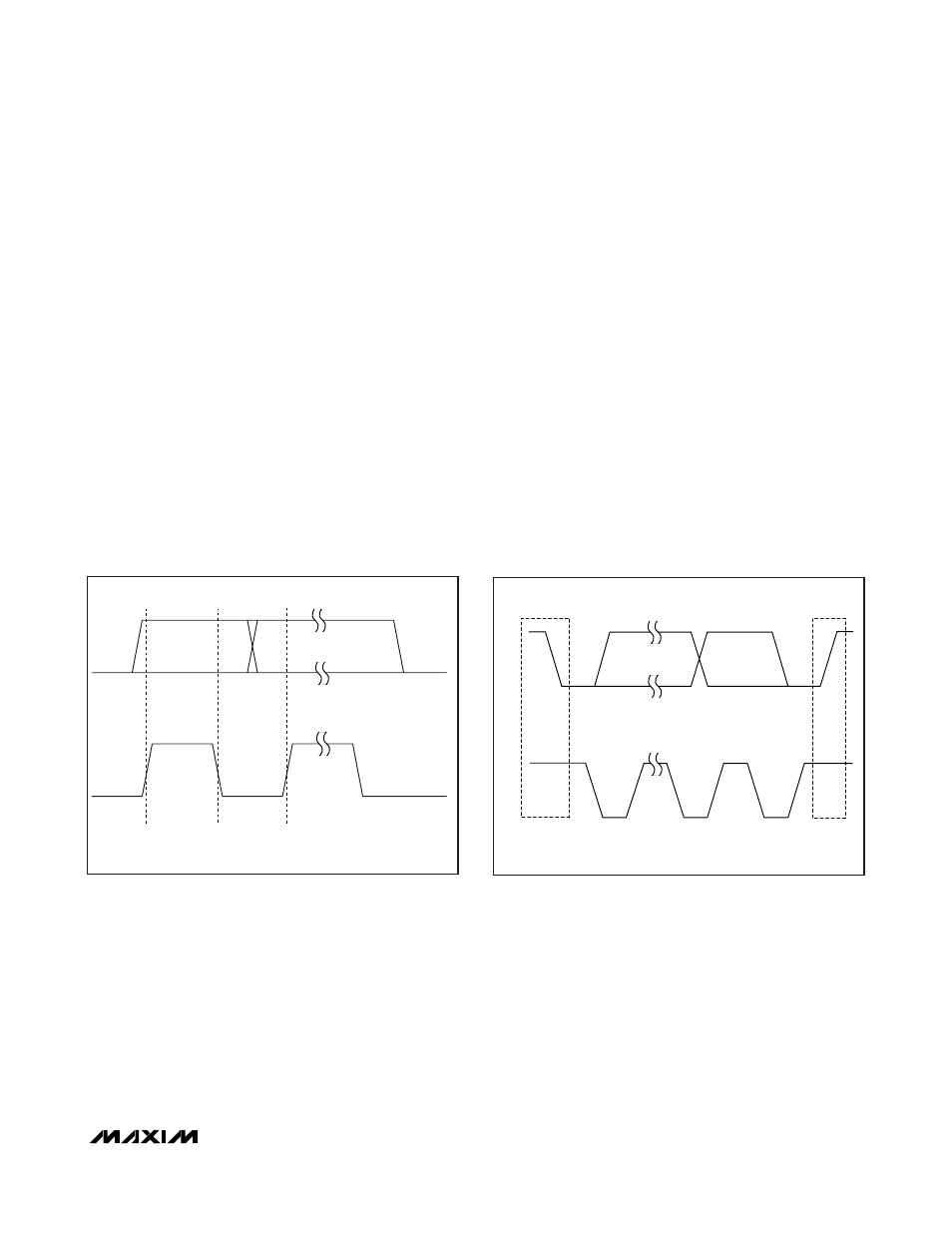

Bit Transfer

Each clock pulse transfers one data bit. The data on

SDA must remain stable while SCL is high (see Figure

6), otherwise the MAX5961 registers a START or STOP

condition (see Figure 7) from the master. SDA and SCL

idle high when the bus is not busy.

START and STOP Conditions

Both SCL and SDA idle high when the bus is not busy.

A master device signals the beginning of a transmis-

sion with a START condition (see Figure 7) by transi-

tioning SDA from high to low while SCL is high. The

master device issues a STOP condition (see Figure 7)

by transitioning SDA from low to high while SCL is high.

A STOP condition frees the bus for another transmis-

sion. The bus remains active if a REPEATED START

condition is generated, such as in the block read proto-

col (see Figure 8).

Early STOP Conditions

The MAX5961 recognizes a STOP condition at any point

during transmission except if a STOP condition occurs

in the same high pulse as a START condition. This con-

dition is not a legal I

2

C format. At least one clock pulse

must separate any START and STOP condition.

REPEATED START Conditions

A REPEATED START condition may indicate a change

of data direction on the bus. Such a change occurs

when a command word is required to initiate a read

operation (see Figure 8). SR may also be used when

the bus master is writing to several I

2

C devices and

does not want to relinquish control of the bus. The

MAX5961 serial interface supports continuous write

operations with or without an SR condition separating

them. Continuous read operations require SR condi-

tions because of the change in direction of data flow.

Figure 6. Bit Transfer

Figure 7. START and STOP Conditions

DATA LINE STABLE,

DATA VALID

SDA

SCL

CHANGE OF

DATA ALLOWED

P

S

START

CONDITION

SDA

SCL

STOP

CONDITION