Rainbow Electronics MAX5961 User Manual

Page 33

MAX5961

0 to 16V, Quad, Hot-Swap Controller

with 10-Bit Current and Voltage Monitor

______________________________________________________________________________________

33

Deglitching of Digital Comparators

The five digital comparators per hot-swap channel

(undervoltage/overvoltage warning and critical, over-

current warning) all have a user-selectable deglitching

feature that requires two consecutive positive com-

pares before the MAX5961 takes action as determined

by the particular compare and the setting of the PROT

input.

The deglitching function is enabled or disabled per

comparator by registers dgl_i, dgl_uv, and dgl_ov

(Tables 38, 39, and 40). Writing a 1 to the appropriate

bit location in these registers enables the deglitch func-

tion for the corresponding digital comparator.

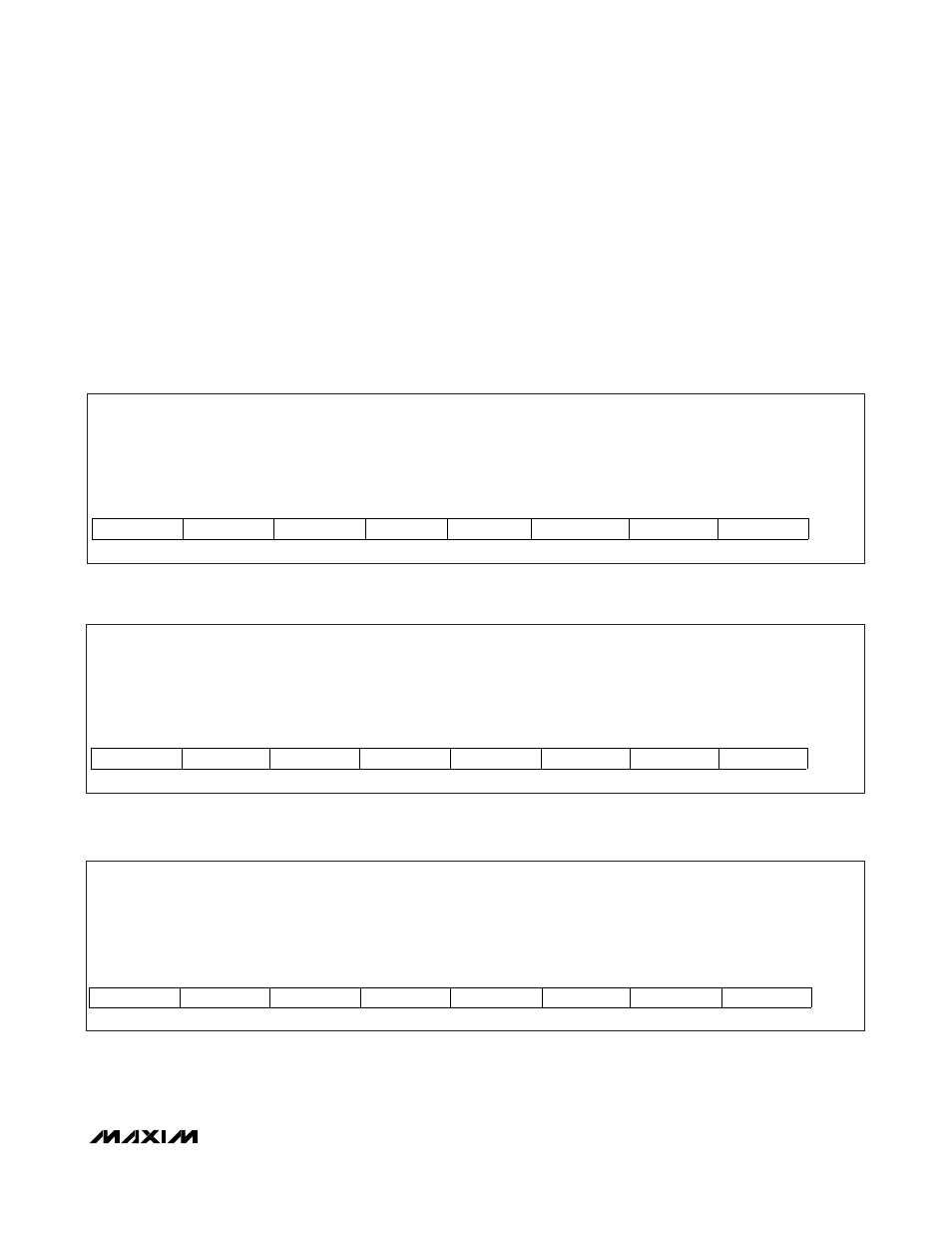

Table 38. OC Warning Comparators Deglitch Enable Register Format

Description:

Deglitch enable register for overcurrent warning digital comparators

Register Title:

dgl_i

Register Address:

0x6A

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

RESET

VALUE

Ch4_dgl_i

Ch3_dgl_i

Ch2_dgl_i

Ch1_dgl_i

0x00

bit 7

bit 6

bit 5

bit 4

bit 3

bit 2

bit 1

bit 0

Table 39. UV Warning and Critical Comparators Deglitch Enable Register Format

Description:

Deglitch enable register for undervoltage warning and critical digital comparators

Register Title:

dgl_uv

Register Address:

0x6B

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

RESET

VALUE

Ch4_dgl_uv2

Ch4_dgl_uv1

Ch3_dgl_uv2

Ch3_dgl_uv1

Ch2_dgl_uv2

Ch2_dgl_uv1

Ch1_dgl_uv2

Ch1_dgl_uv1

0x00

bit 7

bit 6

bit 5

bit 4

bit 3

bit 2

bit 1

bit 0

Table 40. OV Warning and Critical Comparators Deglitch Enable Register Format

Description:

Deglitch enable register for overvoltage warning and critical digital comparators

Register Title:

dgl_ov

Register Address:

0x6C

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

RESET

VALUE

Ch4_dgl_ov2

Ch4_dgl_ov1

Ch3_dgl_ov2

Ch3_dgl_ov1

Ch2_dgl_ov2

Ch2_dgl_ov1

Ch1_dgl_ov2

Ch1_dgl_ov1

0x00

bit 7

bit 6

bit 5

bit 4

bit 3

bit 2

bit 1

bit 0