Rainbow Electronics MAX5961 User Manual

Page 32

MAX5961

0 to 16V, Quad, Hot-Swap Controller

with 10-Bit Current and Voltage Monitor

32

______________________________________________________________________________________

Using the Voltage and

Current Peak-Detection Registers

The voltage and current minimum- and maximum-value

records in register locations 0x10 through 0x2F can be

reset by writing a 1 to the appropriate location in regis-

ter peak_log_rst (see Table 36). The minimum-value

registers are reset to 0x3FF, and the maximum-value

registers are reset to 0x000.

As long as a bit in register peak_log_rst is 1, the corre-

sponding peak-detection registers are disabled and

are “cleared” to their power-up reset values. The volt-

age and current minimum- and maximum-detection

register contents for each signal can be “held” by set-

ting bits in register peak_log_hold (see Table 37).

Writing a 1 to a location in register peak_log_hold locks

the register contents for the corresponding signal and

stops the min/max detection and logging; writing a 0

enables the detection and logging. Note that the peak-

detection registers cannot be cleared while they are

held by register peak_log_hold.

The combination of these two control registers allows

the user to monitor voltage and current peak-to-peak

values during a particular time period.

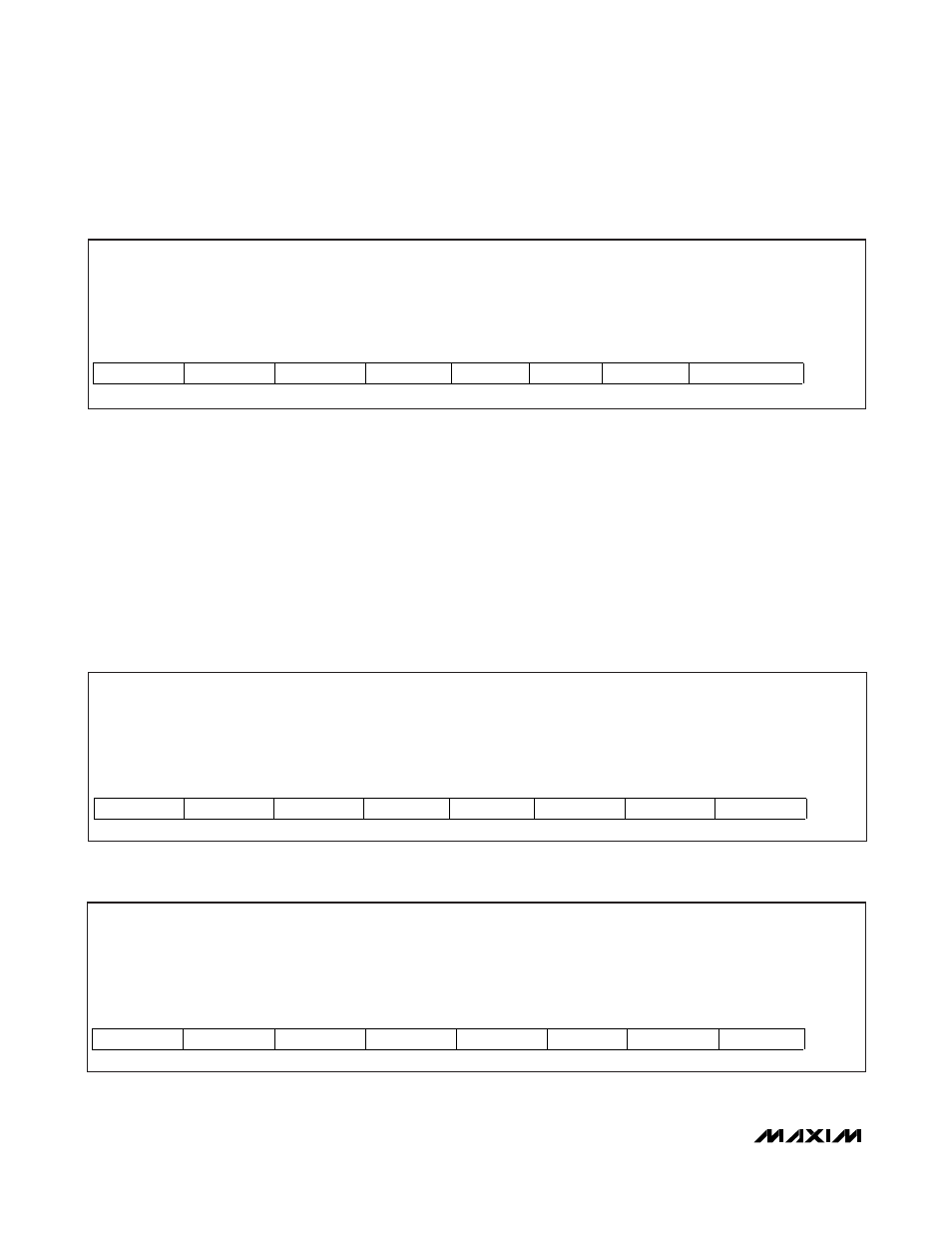

Table 35. ADC Maximum Voltage Conversion Register Format (Low-Order Bits)

Description:

Maximum voltage conversion result, low-order bits [1:0]

Register Titles:

max_ch1_mon_l

max_ch2_mon_l

max_ch3_mon_l

max_ch4_mon_l

Register Addresses:

0x17

0x1F

0x27

0x2F

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

RESET

VALUE

vmax_1

vmax_0

0x00

bit 7

bit 6

bit 5

bit 4

bit 3

bit 2

bit 1

bit 0

Table 36. Peak-Detection Reset-Control Register Format

Description:

Reset control bits for peak-detection registers

Register Title:

peak_log_rst

Register Address:

0x73

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

RESET

VALUE

ch4_v_rst

ch4_i_rst

ch3_v_rst

ch3_i_rst

ch2_v_rst

ch2_i_rst

ch1_v_rst

ch1_i_rst

0x00

bit 7

bit 6

bit 5

bit 4

bit 3

bit 2

bit 1

bit 0

Table 37. Peak-Detection Hold-Control Register Format

Description:

Hold control bits for peak-detection registers; per signal

Register Title:

peak_log_hold

Register Address:

0x74

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

RESET

VALUE

ch4_v_hld

ch4_i_hld

ch3_v_hld

ch3_i_hld

ch2_v_hld

ch2_i_hld

ch1_v_hld

ch1_i_hld

0x00

bit 7

bit 6

bit 5

bit 4

bit 3

bit 2

bit 1

bit 0