Table 9 clocks as differential pairs – Nortel Networks NN43001-318 User Manual

Page 42

42

Installing ISDN BRI hardware

The SILC can recover the network clock from the received data stream

using on-chip phase lock loops. The clock frequency that is recovered is

2.56 MHz. The jitter and wander conform to CCITT recommendations.

All of the S/T chips on the SILC could be configured as Terminal Equipment

Slaves (TES), but only the clocks recovered from DSL0 and DSL1 are

routed to the back plane connector pins. These clocks are provided as

differential pairs on back plane pins. See

Table 9 "Clocks as differential

.

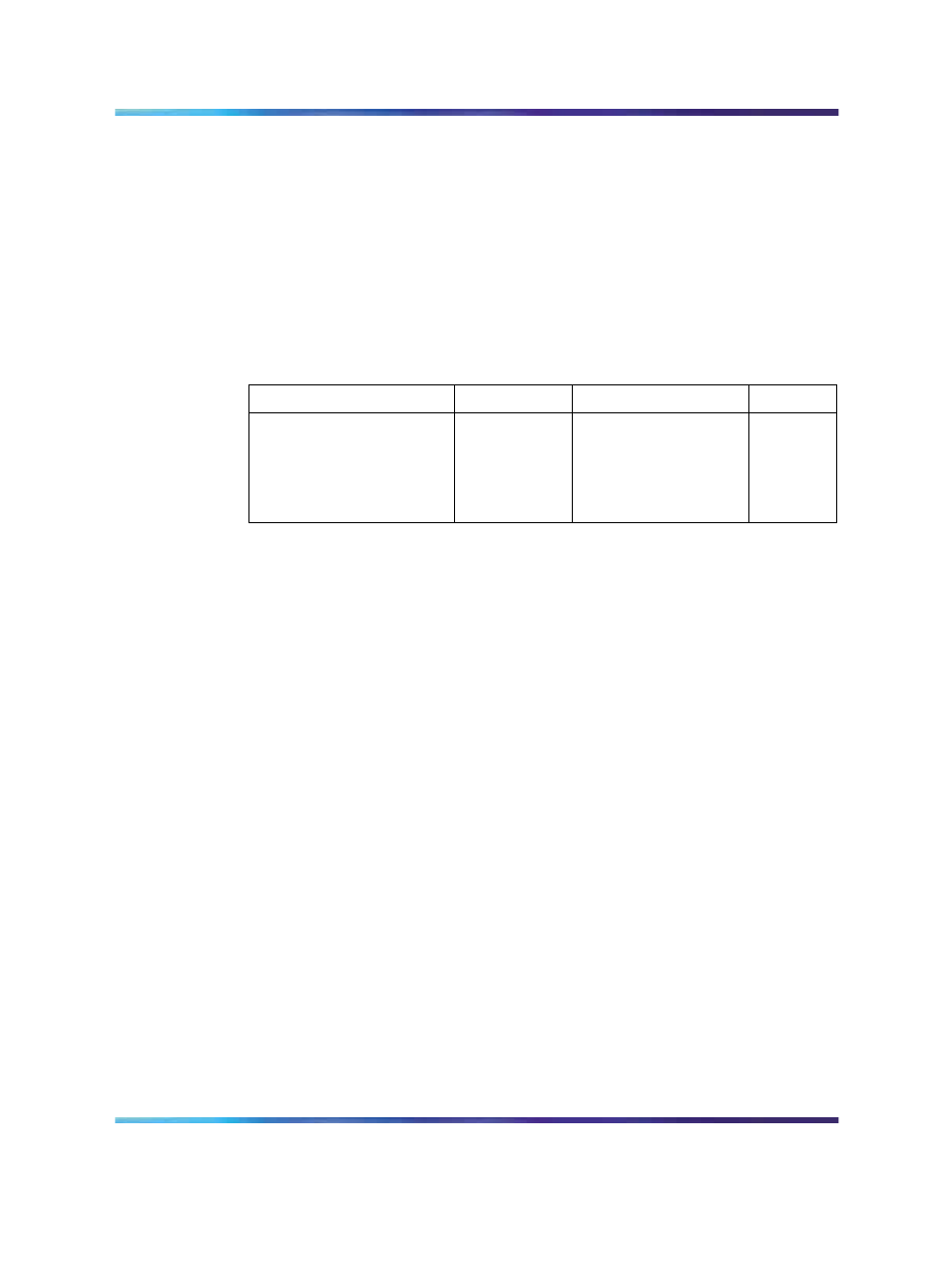

Table 9

Clocks as differential pairs

Differential pairs

Pin #

Row A

Row B

Primary

73

+Ref 0A

- Ref 0A

Primary

74

+Ref 1A

- Ref 1A

Secondary

75

+Ref 0B

- Ref 0B

Secondary

76

+Ref 1B

- Ref 1A

Automatic clock recovery is done upon the expiration of the free run guard

timer. Tracking is restored to the primary reference clock, if defined. If the

primary reference clock is disabled, tracking is restored to the secondary

reference clock, if defined.

Installing the SILC and the UILC

Follow the same procedures as described earlier for line applications (refer

to

Procedure 5 "Installing the BRSC, SILC, and UILC" (page 22)

Connecting the system to the Main Distribution Frame (MDF)

Follow the same procedures as described earlier for line applications (refer

to

Procedure 8 "Connect the modules to the MDF" (page 24)

Cross-connecting the Main Distribution Frame (MDF)

The system, in TIE trunk or CO connectivity, requires a different wiring

configuration than for a line application; the transmit and receive pairs should

be reversed, as illustrated in

Figure 12 "Connect the network termination to

the U interface and to the S/T interface (in TE mode)" (page 43)

Nortel Communication Server 1000

ISDN Basic Rate Interface Installation and Commissioning

NN43001-318

01.02

Standard

Release 5.0

20 June 2007

Copyright © 2003-2007, Nortel Networks

.