3 memory, Memory – Intel OCPRF100 MP User Manual

Page 125

OCPRF100 MP Server System Technical Product Specification

Revision 1.0

118

NOTE:

The programmable logic device (PLD) addresses are calculated using offset term and the following equation:

ADDRESS = PLD_BASE + OFFSET * 80H

10.2.3

Memory

10.2.3.1

Program Memory, Flash

The front panel contains an ATMEL 29C512* for storing program memory and initialized vari-

ables. This device is nominally 64KB by 8 but is expandable to 128KB by 8. In order to use the

128KB by 8 devices, the memory model would need to be changed to provide enough address

space, or a paging scheme would need to be incorporated.

FRU information is not stored in this device, but, rather, is stored in the serial EEPROM.

10.2.3.2

RAM

There is 32KB by 8 of RAM on the FPC. Note that only approximately 7.5KB of the RAM is

accessible according to the memory map.

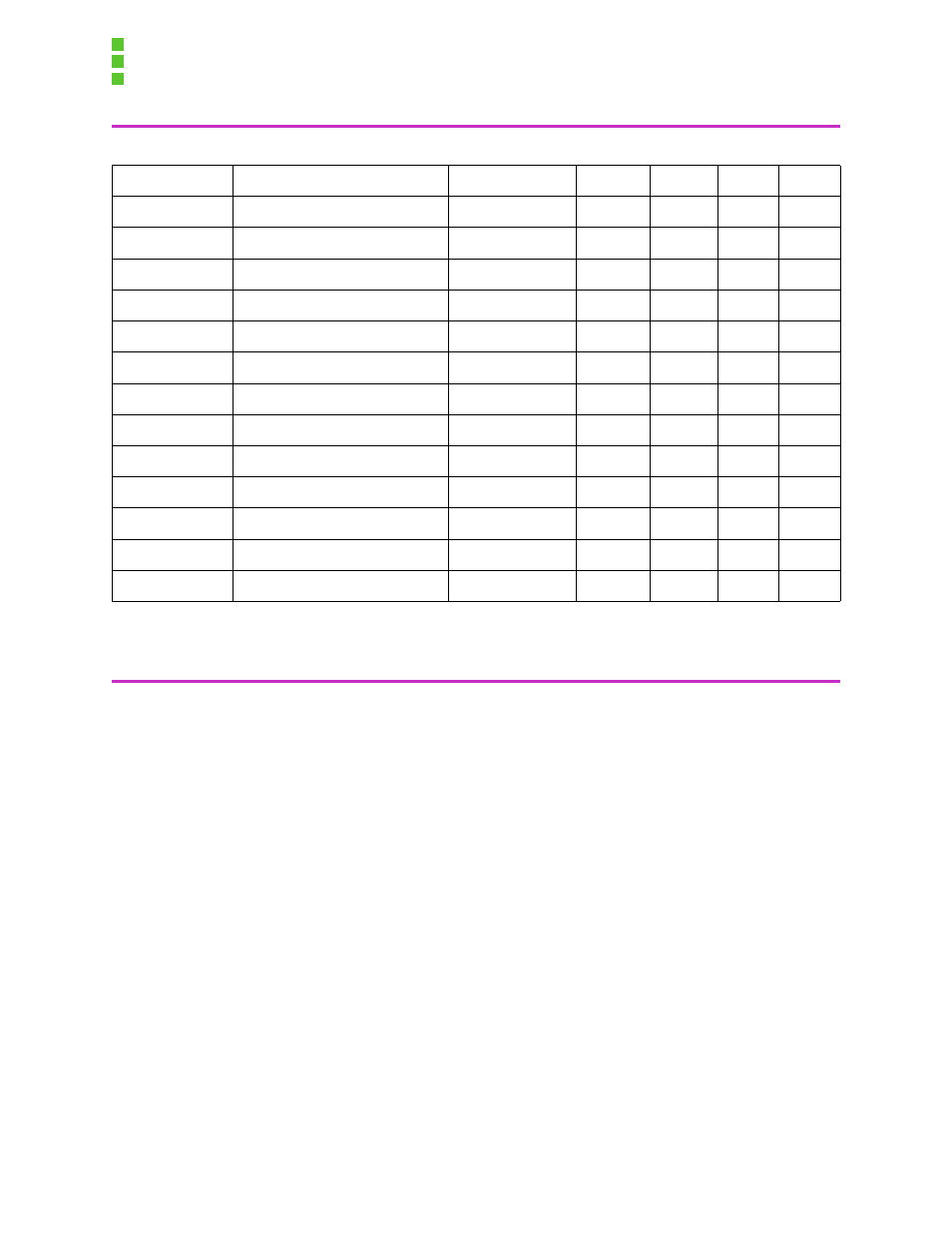

COM2/ICMB

COM2_ACTIVITY_LATCH

PLD

FED0

RW

13

0

Memory

I2C_CEL_CONNECT_FPC

PLD

FEC0

RW

12

0

Memory

I2C_CEL_CONNECT_BMC

PLD

FEB0

RW

11

0

System Power

PWR_GOOD_LATCH

PLD

FEA0

RW

10

0

COM2/ICMB

ICMB_EN_LATCH

PLD

FE90

RW

9

0

COM2/ICMB

FORCE_RXD_ICMB_LATCH

PLD

FE80

RW

8

0

COM2/ICMB

FORCE_RXD_COM2_LATCH

PLD

FE70

RW

7

0

Reserved

Reserved

PLD

FE60

RW

6

0

SPEAKER

SPEAKER_LATCH

PLD

FE50

RW

5

0

System Power

PWR_RTC_TRANS_LATCH

PLD

FE40

RW

4

0

System Power

PWR_SFC_LATCH

PLD

FE30

RW

3

0

System Power

PWR_SWT_LATCH

PLD

FE20

RW

2

0

System Power

PWR_INTR_LATCH_L

PLD

FE10

RW

1

0

Memory Map

UART_INT

PLD

FE00

RW

0

0

Table 10-2: I/O Signals and Devices