3 j1850 controller operation, 1 control state machine, 1 cyclic redundancy check generator – Intel 8XC196Lx User Manual

Page 70: J1850 controller operation -4, Control state machine -4, Cyclic redundancy check generator -4

8XC196L

X SUPPLEMENT

8-4

8.3

J1850 CONTROLLER OPERATION

This section describes the control state machine (which contains the cyclic redundancy check

generator) and the symbol synchronization and timing circuitry for J1850 transmissions and re-

ceptions.

8.3.1

Control State Machine

The control state machine (CSM) represents the engine of the digital circuitry portion of the

J1850 communications controller. The CSM handles all message framing for standard and in-

frame response (IFR) messaging, data validation, bus contention, bit arbitration, and error detec-

tion.

8.3.1.1

Cyclic Redundancy Check Generator

The cyclic redundancy check (CRC) generator circuitry calculates and checks the CRC byte gen-

erated for both transmitted and received standard messages as specified by SAE J1850 protocol

specification for class B in-vehicle networks. The CRC calculation is a code byte of information

that verifies the proper reception or transmission of your message. The calculated CRC code byte

is always appended as the last byte of your transmitted message. On reception, the calculated

CRC checksum byte always results in a value of C4H for valid messages. An invalid CRC check-

sum during reception signals the presence of an error in your incoming message, which immedi-

ately sets the J1850 bus error (J1850BE) bit in the J_STAT register (Figure 8-19 on page 8-21).

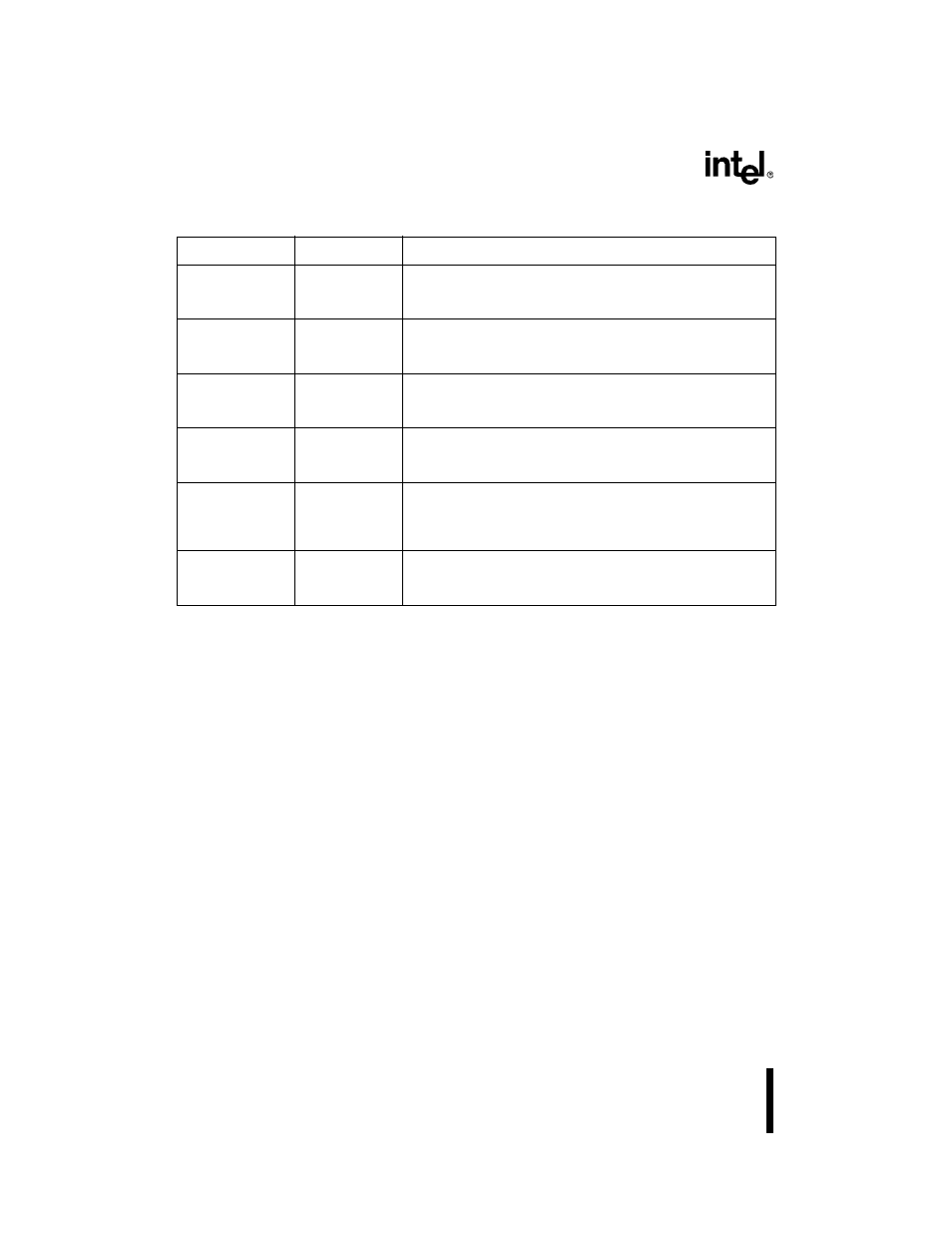

INT_MASK

0008H

Interrupt Mask

Bits 6 and 7 in this register enable and disable the J1850 receive

and transmit interrupt requests, respectively.

INT_MASK1

0013H

Interrupt Mask 1

Bit 0 in this register enables and disables the J1850 bus error

interrupt request.

INT_PEND

0009H

Interrupt Pending

Bits 6 and 7 in this register, when set, indicate pending J1850

receive and transmit interrupt requests, respectively.

INT_PEND1

0012H

Interrupt Pending 1

Bit 0 in this register, when set, indicates a pending J1850 bus

error interrupt request.

PTSSEL

0004H

PTS Select

Bits 6, 7, and 8 of this word register select either a PTS service

request or a standard interrupt service request for J1850TX,

J1850RX, and J1850ST interrupts, respectively.

PTSSRV

0006H

PTS Service

Bits 6, 7, and 8 of this word register are set by hardware to

request an end-of-PTS interrupt for the J1850.

Table 8-2. Control and Status Registers (Continued)

Mnemonic

Address

Description