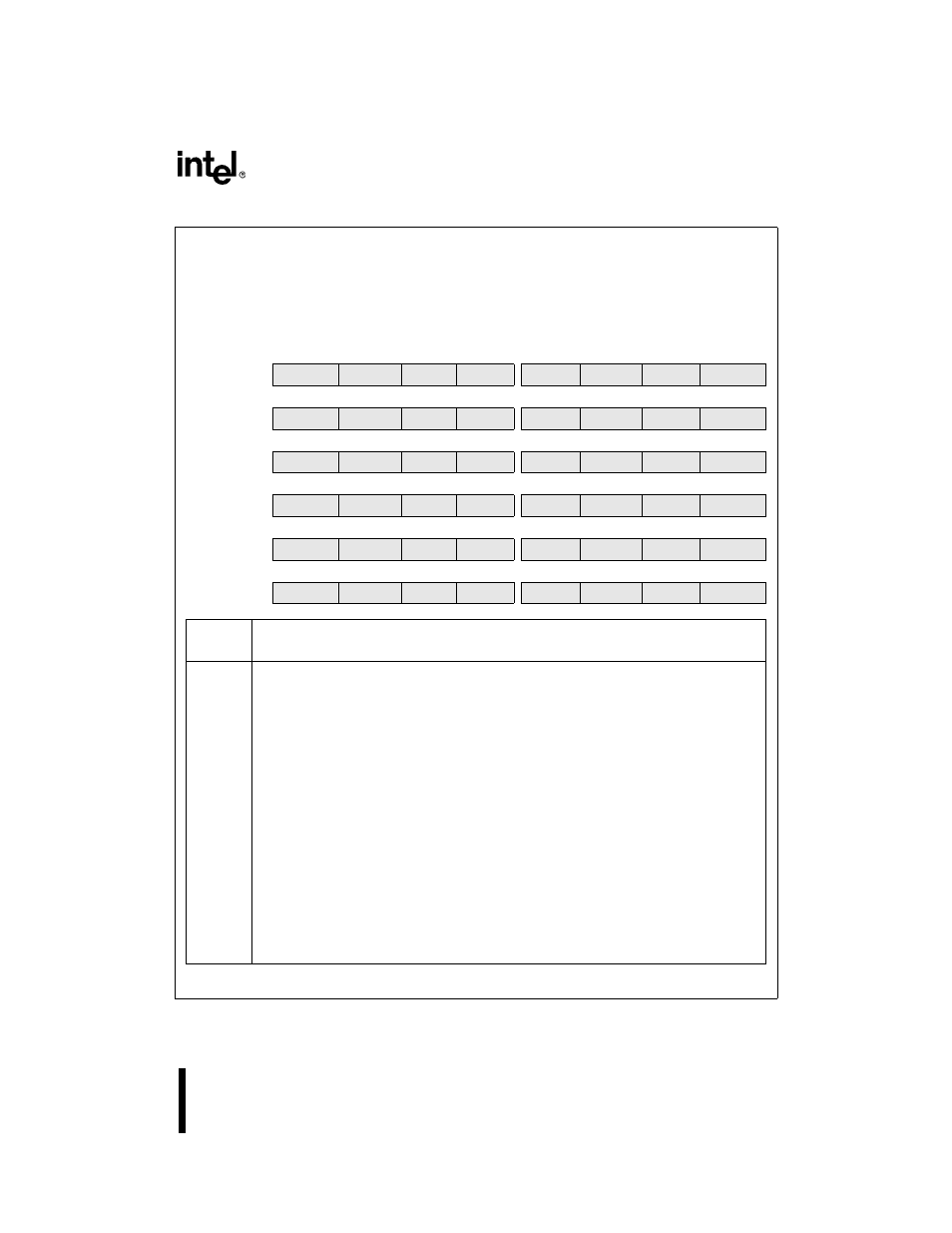

Figure 45. pts select (ptssel) register, Pts select (ptssel) register -7 – Intel 8XC196Lx User Manual

Page 41

4-7

STANDARD AND PTS INTERRUPTS

PTSSEL

Address:

Reset State:

0004H

0000H

The PTS select (PTSSEL) register selects either a PTS microcode routine or a standard interrupt

service routine for each interrupt request. Setting a bit selects a PTS microcode routine; clearing a bit

selects a standard interrupt service routine. In PTS modes that use the PTSCOUNT register, hardware

clears the corresponding PTSSEL bit when PTSCOUNT reaches zero. The end-of-PTS interrupt service

routine must reset the PTSSEL bit to re-enable the PTS channel.

15

8

LA

—

EXTINT

—

RI

TI

SSIO1

SSIO0

—

7

0

—

—

AD

EPA0

EPA1

EPA2

EPA3

EPA

x

15

8

LB

—

EXTINT

—

RI

TI

SSIO1

SSIO0

J1850ST

7

0

J1850RX

J1850TX

AD

EPA0

EPA1

EPA2

EPA3

EPA

x

15

8

LD

—

EXTINT

—

RI

TI

SSIO1

SSIO0

—

7

0

—

—

—

EPA0

EPA1

EPA2

EPA3

EPA

x

Bit

Number

Function

14:0

†

Setting a bit causes the corresponding interrupt to be handled by a PTS microcode routine.

The PTS interrupt vector locations are as follows:

Bit Mnemonic

Interrupt

PTS Vector

EXTINT

EXTINT pin

205CH

Reserved

†

—

205AH

RI

SIO Receive

2058H

TI

SIO Transmit

2056H

SSIO1

SSIO 1 Transfer

2054H

SSIO0

SSIO 0 Transfer

2052H

J1850ST (LB)

J1850 Status

2050H

J1850RX(LB)

J1850 Receive

204EH

J1850TX(LB) J1850 Transmit

204CH

AD (LA, LB)

A/D Conversion Complete

204AH

EPA0

EPA Capture/Compare Channel 0

2048H

EPA1

EPA Capture/Compare Channel 1

2046H

EPA2

EPA Capture/Compare Channel 2

2044H

EPA3

EPA Capture/Compare Channel 3

2042H

EPA

x

††

Multiplexed EPA

2040H

††

PTS service is not useful for shared interrupts because the PTS cannot readily

determine the source of these interrupts.

†

Bit 13 is reserved on the 8XC196L

x devices and bits 6–8 are reserved on the 87C196LA and

83C196LD. For compatibility with future devices, write zeros to these bits.

Figure 4-5. PTS Select (PTSSEL) Register