3 outline of the frame information structure (fis) – FUJITSU MHW2120BS User Manual

Page 91

5.2 Logical Interface

5.2.3 Outline of the frame information structure (FIS)

The transport layer converts data written in a Block Register into the FIS, and

sends it to the upper layer.

The FIS, which is generated in the transport layer, is explained below.

5.2.3.1 FIS types

The types of FIS are as follows (Each FIS is referred to as abbreviation in square

brackets in this manual.):

•

Register- Host to Device [RegHD]

•

Register- Device to Host [RegDH]

•

DMA Active – Device to Host [DMA Active]

•

DMA Setup – Device to Host or Host to Device (Bidirectional)

[DMA Setup]

•

Set Device Bits – Device to Host [SetDB]

•

BIST Active – Bidirectional [BIST Active]

•

PIO Setup – Device to Host [PIO Setup]

•

Data – Host to Device or Device to Host (Bidirectional) [DATA]

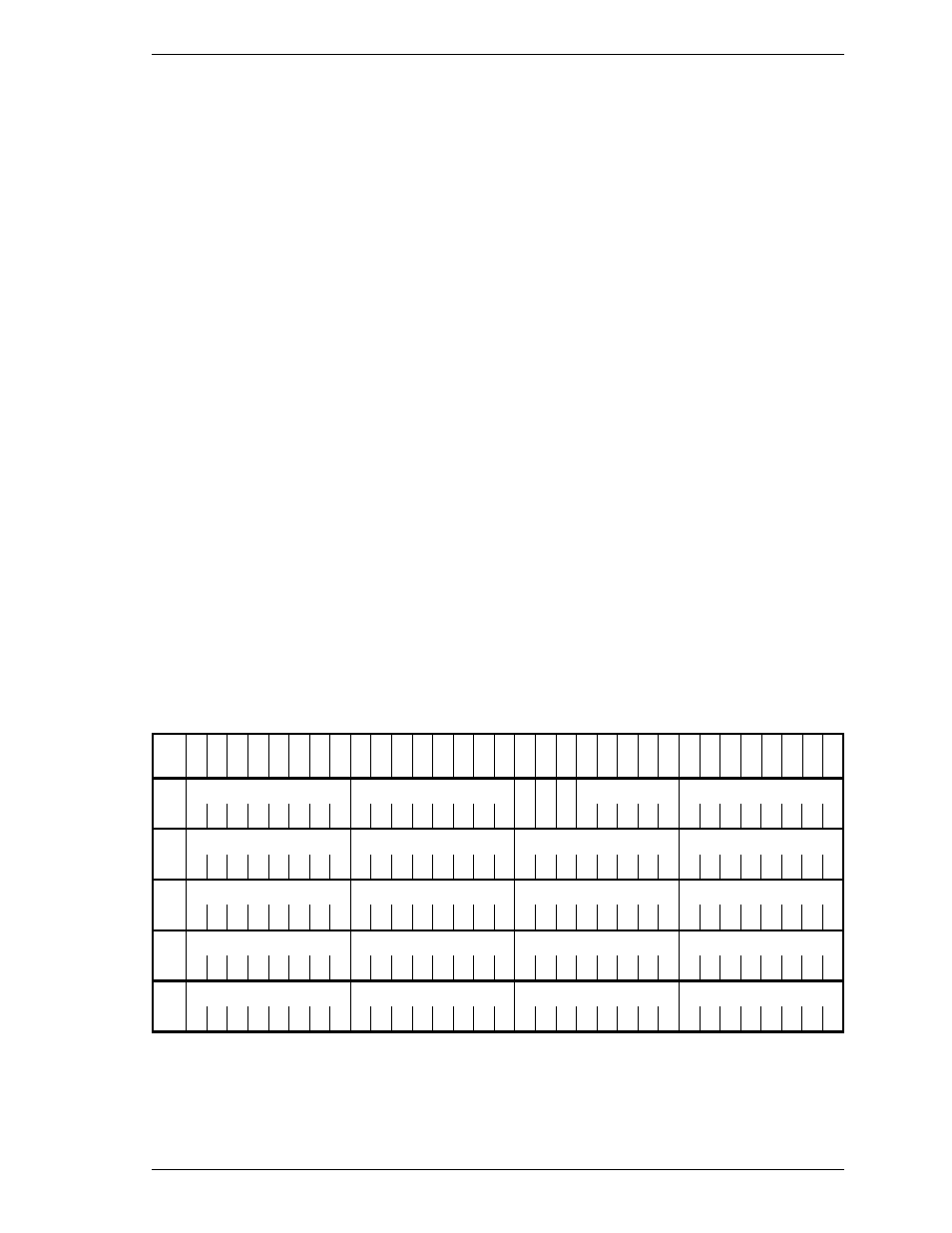

5.2.3.2 Register - Host to Device

The Register - Host to Device FIS has the following layout:

31

3

0

2

9

2

8

2

7

2

6

2

5

2

4

2

3

2

2

2

1

2

0

1

9

1

8

1

7

1

6

1

5

1

4

1

3

1

2

1

1

1

0

9 8 7 6 5 4 3 2 1 0

Features

Command

C R R Reserved (0)

FIS Type (27h)

0

Device

LBA High

LBA Mid

LBA Low

1

Features (exp)

LBA High (exp)

LBA Mid (exp)

LBA Low (exp)

2

Control

Reserved (0)

Sector Count (exp)

Sector Count

3

Reserved (0)

Reserved (0)

Reserved (0)

Reserved (0)

4

Figure 5.4 Register - Host to Device FIS layout

C141-E249

5-17