4 digital pod registers, 5 digital ios output register – Sundance SMT321 User Manual

Page 26

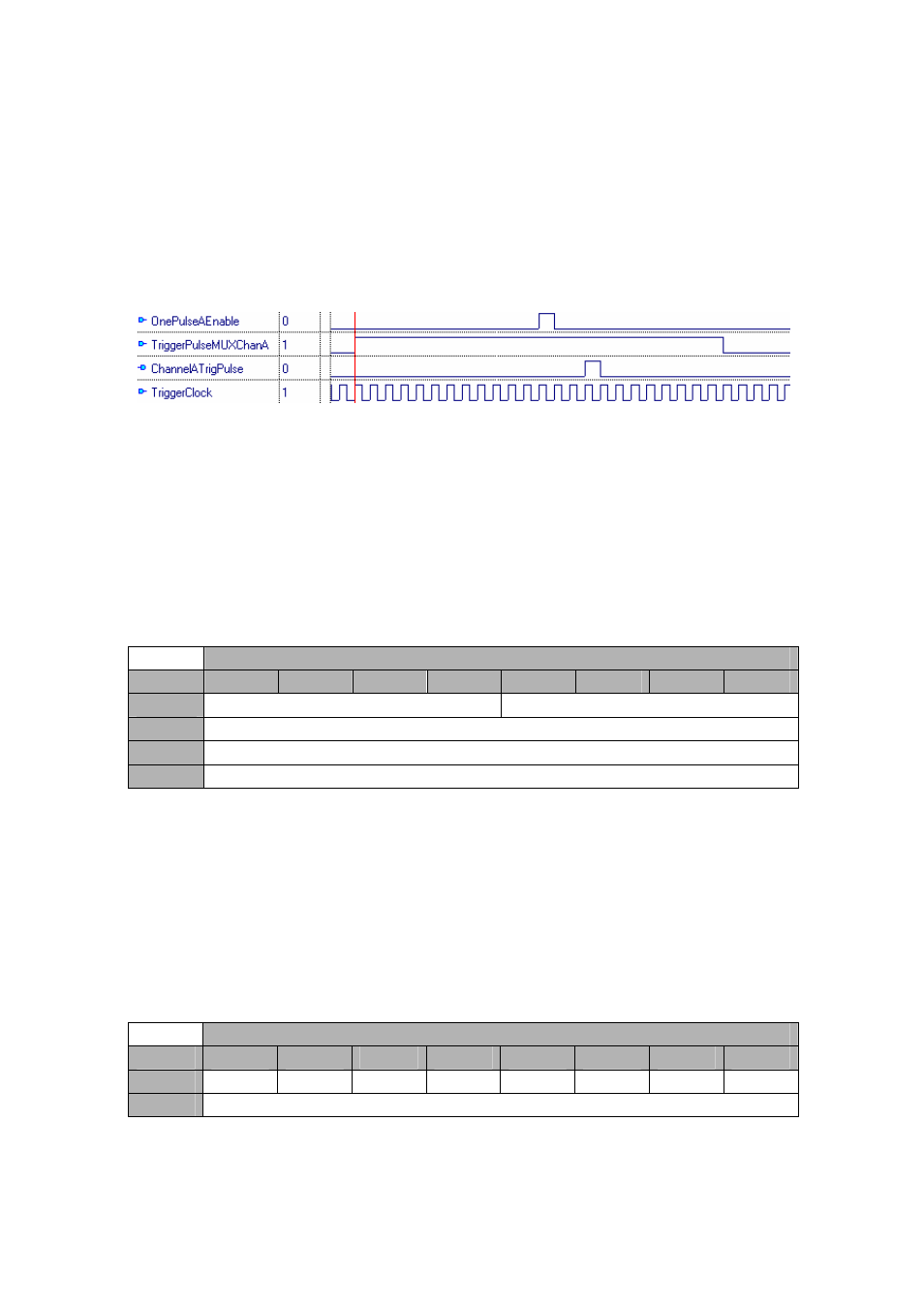

The channel can be switch between continuous trigger and pulse with the last two

registers,

Trigger Pulse Multiplexers registers 0x026 and 0x027. If a 1 is written into any

of the two that specific channel switches to one pulse generation. If a 0 is written into the

register it switches to continuous trigger for the specific channel. Figure 15 shows how a

one pulse is enabled on the channel.

Figure 15. One pulse generated on trigger A output (ChannelATrigPulse).

If another pulse is needed the pulse high register value must be written again.

4.4.4 Digital Pod Registers

These writable registers are the digital pod control registers. As explained earlier in the

document to configure the digital pod a 24bit data word is needed which is clocked into

the pod. The comports however can only transmit 16 bits of data at a time so two

registers is used and thus an 8 bit waste in the last register. Table 9 shows the two 16 bit

registers contents. The MSB register contains the command, address and data bits. The

LSB register only contains the last 8 bits of data from the word.

Digital Pod Register

Byte

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

0 (MSB)

Command

Address

1 (MSB)

Data

2 (LSB)

Data

3 (LSB)

NO CARES

Table 9. Digital pod register setup.

These registers are then combined and the last 8 bits left out making a 24 bit word in

firmware which is then clocked into the digital pod.

For more information refer to the Analog Devices digital pod datasheets [3].

4.4.5 Digital IOS output register

This writeable register allows the host to pull the 8 digital IOS present on the SMT321

high or low. Only the first byte (MSB) is used. The packet is shown in table 10.

Digital IOS Register

Byte

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

0 (MSB)

Dig IO 7

Dig IO 6

Dig IO 5

Dig IO 4

Dig IO 3

Dig IO 2

Dig IO 1

Dig IO 0

1 (LSB)

NO CARES

Table 10. Digital IO register setup.