Sundance SMT321 User Manual

Page 23

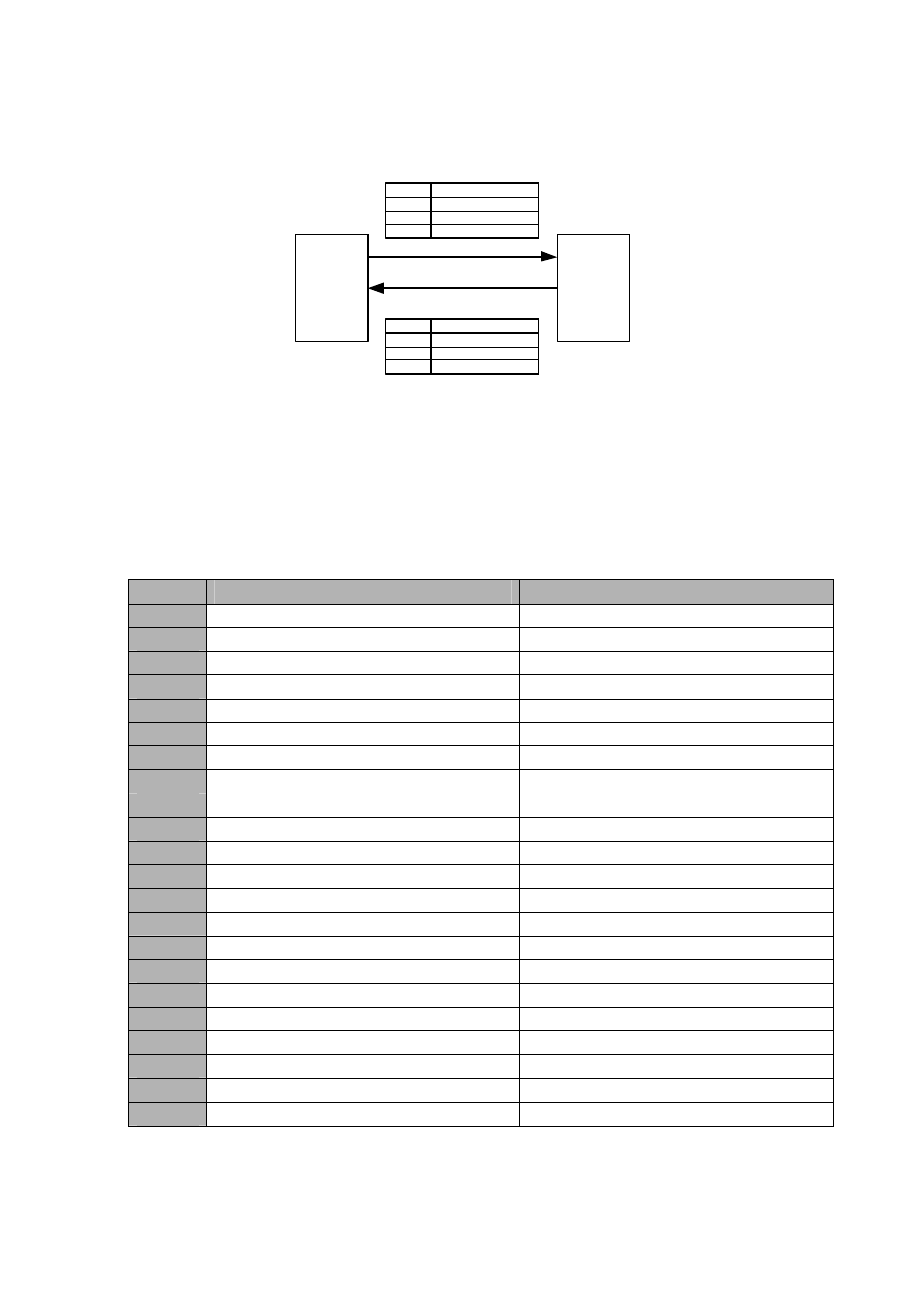

Host

Command/Address

SMT321

ComPort 3

ComPort 0

Byte 0

Address

Byte 1

Write Data

Byte 3

Write Data

Byte 4

1) Write Packet

Command/Address

Byte 0

Address

Byte 1

Read Data

Byte 3

Read Data

Byte 4

2) Read Packet

Figure 12. Control Register Read Sequence.

4.3 Memory Map

The write packets must contain the address where the data must be written to and the

read packets must contain the address where the required data must be read. The

following table shows the memory map for the writable and readable Control Registers

on the SMT321:

Address

Writable Registers

Readable Registers

0x000

Reserved

Firm Ware Version

0x001

Com In Scratch Register 0

Com Out Scratch Register 0

0x002

Com In Scratch Register 1

Com Out Scratch Register 1

0x003

Reserved

Smt321 Serial Number A Register

0x004

Reserved

Smt321 Serial Number B Register

0x005

Reserved

Smt321 Serial Number C Register

0x006

Reserved

Smt321 Serial Number D Register

0x007

Reserved

Smt321 Air Temp

0x008

Reserved

Smt321 Diode Temp

0x009

Reserved

Smt321 D1V2 Register

0x00A

Clock Control Register A

Smt321 D2V5 Register

0x00B

Clock Control Register B

Smt321 D3V3 Register

0x00C

Reserved

Smt321 D5V0 Register

0x00D

Reserved

FPGA Dip Register

.

Reserved

Reserved

.

Reserved

Reserved

0x020

Trigger A High Register

Reserved

0x021

Trigger A Low Register

Reserved

0x022

Trigger B High Register

Reserved

0x023

Trigger B Low Register

Reserved

0x024

One Pulse A High Register

Reserved

0x025

One Pulse B High Register

Reserved