11 fpga ios, 2 digital ios, 3 trigger connectors – Sundance SMT321 User Manual

Page 18: 4 analog signal connectors, 5 clock connectors

2.10.2 Digital IOS

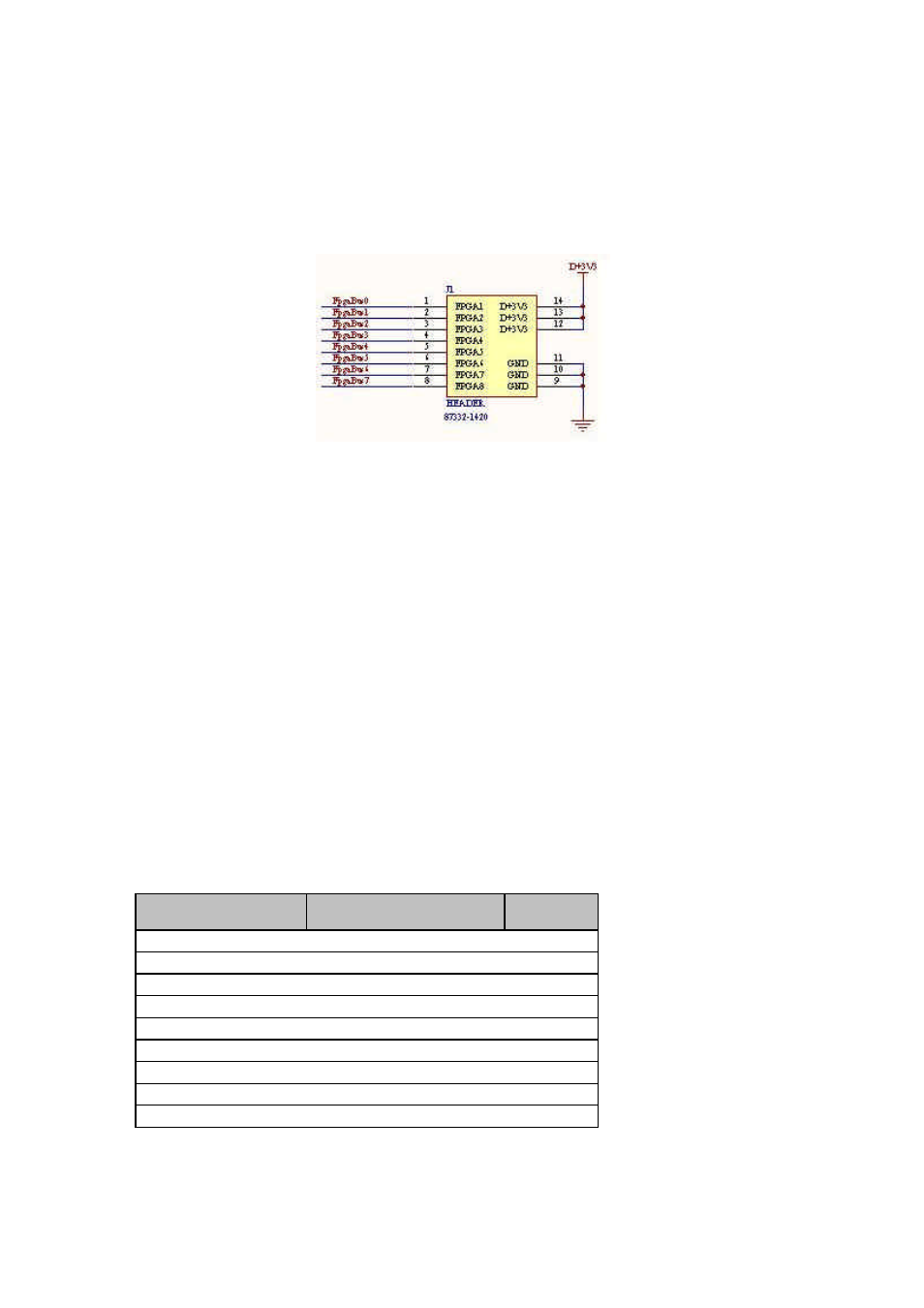

This connector has 14 pins with 8 pins directly connected to a register in the FPGA. The

remaining 6 pins are split up into 3 pins for 3V3 and 3 pins connected to GND. Figure 10

shows the pin assignments on the digital IOS connector.

Figure 10. Digital IOS connector present on the SMT321.

2.10.3 Trigger Connectors

Two trigger output connectors. These triggers are LVPECL thus no ground termination

must be present when implementing or measuring the signal.

2.10.4 Analog Signal Connectors

Two analog signal output connectors. These outputs are analog.

2.10.5 Clock Connectors

Two clock output connectors. These clocks are LVPECL thus no ground termination

must be present when implementing or measuring the signal.

2.11 FPGA IOS

Table 4 shows all of the FPGA’s user IOS. All pins are io standard LVTTL.

Pin Number (IOS

only)

Pin Description

IO

Standard

1

Trigger output A

LVTTL

2

Trigger output B

LVTTL

4

Fpga to Dip switch 5

LVTTL

5

Tim Connector 1

LVTTL

6

Tim Connector 2

LVTTL

7

Tim Connector 3

LVTTL

8

Tim Connector 4

LVTTL

10

Tim Connector 5

LVTTL

11

Tim Connector 6

LVTTL