Description of the registers, Accessing the registers – Sundance SMT391-VP User Manual

Page 19

Version 1.3

Page 19 of 41

SMT391-VP User Manual

Description of the registers

The registers in the SMT391-VP firmware control the complete functionality of the

SMT391-VP.

These registers are configured via the comport 3 of the module.

Accessing the registers

It is possible to read and to write the registers of the SMT391-VP. When a write

access occurs the received data is stored into the selected register. When a read

access occurs, the SMT391-VP sends the content of the selected register to the

comport 3.

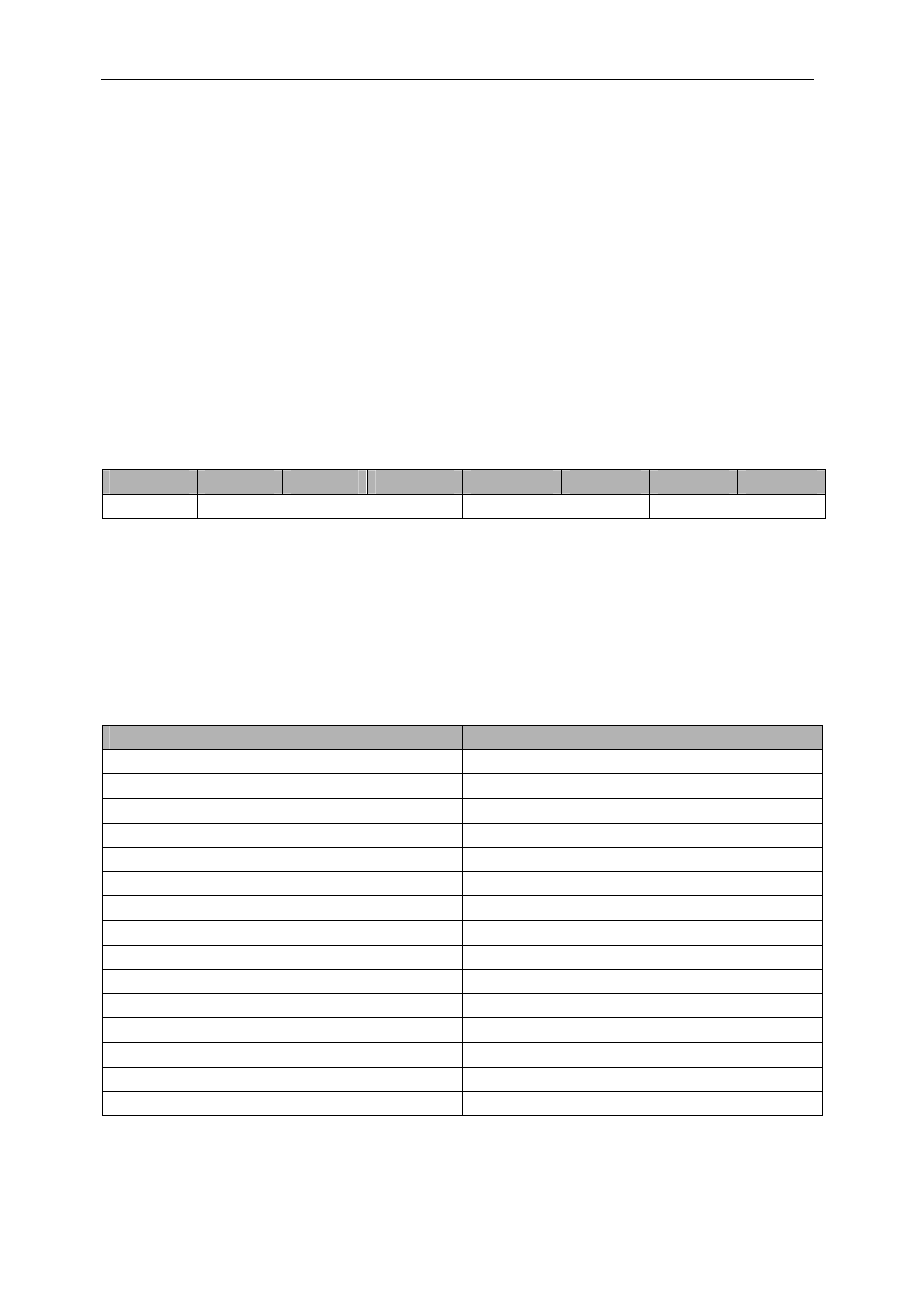

The data sent to the comport 3 of the SMT391-VP follows a certain format used to

specify the type of access requested and the address of the access. The data is mad

of a command, an address and a data. The following figure describes this format:

31 .. 28

27 .. 24

23 .. 20

19 .. 16

15 .. 12

11 .. 8

7 .. 4

3 .. 0

Command

Address

Data MSB

Data LSB

Figure 3 – Setup Packet Structure.

All maximum size of registers that can be written to or read is 16 Bits. When

performing a read bits 31 downto 16 will reflect the command and address. The lower

16 bits will contain the actual data.

The defined commands are:

Command Value

Command Description

0x0 Reserved

0x1 FGPA

Write

0x2 FPGA

Read

0x3 Reserved

0x4 Reserved

0x5 Reserved

0x6 Reserved

0x7 Reserved

0x8 Reserved

0x9 Reserved

0xA Reserved

0xB Reserved

0xC Reserved

0xD Reserved

0xE Reserved