5 applications, 1 incremental encoder interface, 2 pulse generator – Sensoray 2600 User Manual

Page 60

2600 Family Instruction Manual

55

Chapter 9 : Model 2620 Counter Module

Response

(Counts[0]),(Counts[1]),

(Counts[2]),(Counts[3]),

(Tstamp[0]),(Tstamp[1])

Notes

Counting is not interrupted by this action.

9.5 Applications

This section explains how to configure the counter channels for

various common applications.

9.5.1 Incremental Encoder Interface

This configures a counter channel so that it will interface to

either a quadrature-encoded or a single-phase clock source,

with optional index input.

Quadrature-encoded sources are typically used to track the

physical position of a mechanical process that can dither or

travel in two directions, while single-phase sources are for

mechanical processes that travel in only one direction (and

where dithering is either not possible or is not a problem).

The counter core can be forced to a reference value by

triggering a transfer from the Preload0 register. The index

input may be used as a hardware trigger by connecting it to an

external “home position” sensor (e.g., hall-effect sensor,

encoder index output, etc.). If enabled, an index transition will

preload the counter core. The core can always be preloaded by

invoking a SoftTrigger action with the LOD bit asserted.

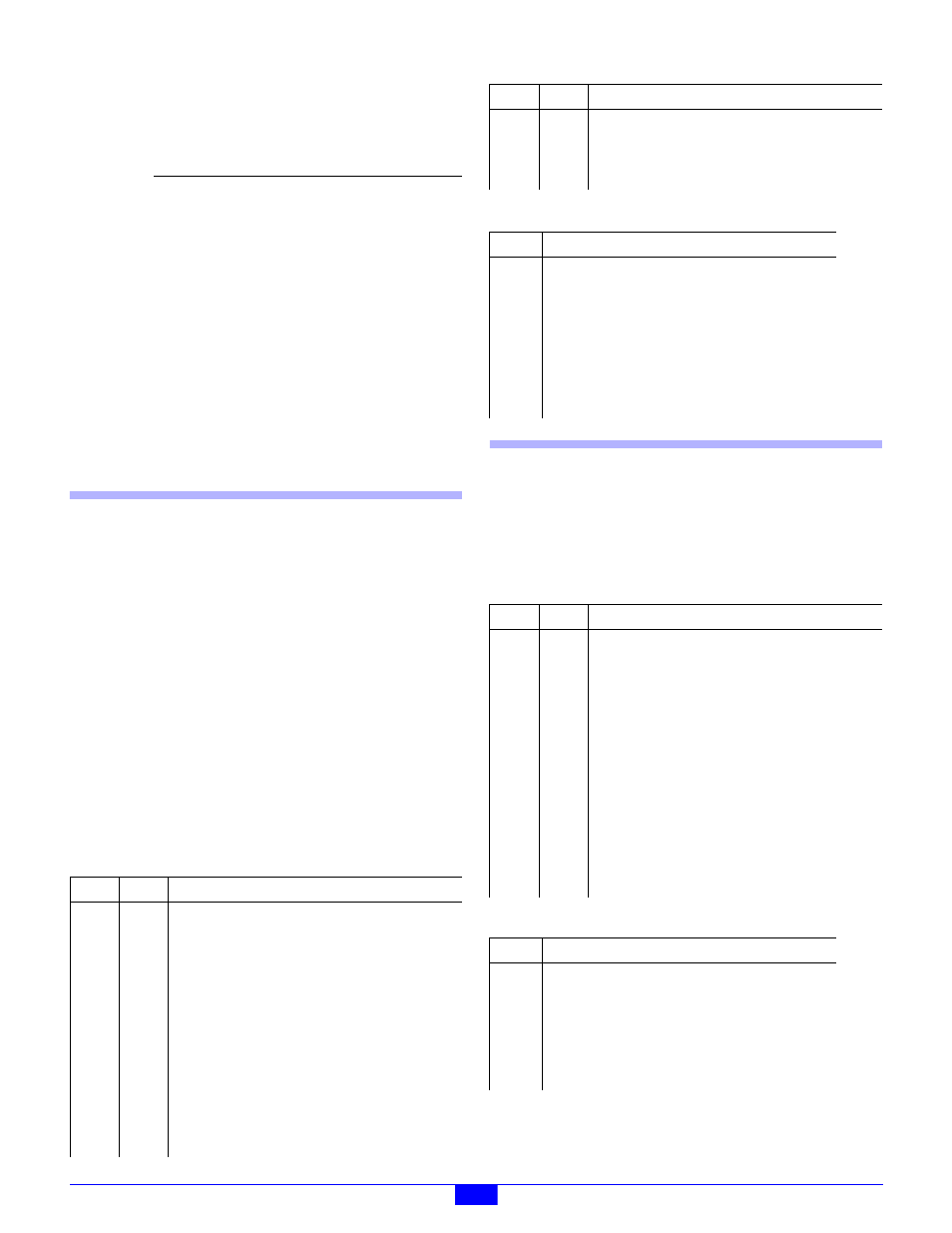

Set the Mode register as follows:

Connect the channel as follows:

9.5.2 Pulse Generator

This configures a counter channel so that it will generate a

single output pulse in response to a hardware or software

trigger (i.e., a “one-shot”). The duration of the output pulse is

determined by the value stored in the Preload0 register.

Set the Mode register as follows:

Connect the channel as follows:

Parameter

Function

Counts

Byte array containing the 32-bit value

that is contained in the counter’s output

latch when the action executes. Bytes

are ordered least-significant byte first.

Tstamp

Byte array contains the 16-bit value

that is contained in the counter’s time

stamp latch when the action executes.

Bytes are ordered least-significant byte

first.

Field Value

Notes

OM

X

XP

*

Set as appropriate if using external index to trigger

preloads.

PL

*

Set to 1 to enable preloads upon external index, or

to 0 for soft preloads only.

LAT

0

Latch on soft trigger.

CET

0

OP

X

M

*

Single-phase clock: set to 4, 5 or 6. Quadrature

clock: set to 0 or 1 (x1 multiplier), 2 (x2

multiplier) or 3 (x4 multiplier).

CD

0

PLM

0

Use only the Preload0 register. Preload0 must be

programmed to the value that will be preloaded

upon preload trigger.

XC

0

External index signal.

Signal

Connect To

ClkA

Clock input for single-phase clocks. For

quadrature clocks, this is the phase-A input.

ClkB

Phase-B input for quadrature clocks. Tie to either

GND or +5V (same as open) to set count direction.

Index

Hardware trigger for preloads. Leave

disconnected if hardware-triggered preloads are

not required.

Output

NC

Field Value

Notes

OM

2

Output active only during pulse.

XP

*

Set as appropriate if using hardware trigger.

PL

*

Set to 1 to enable preloads upon external index, or

to 0 for soft preloads only.

LAT

0

Latch on soft trigger.

CET

0

OP

*

Set output polarity as required.

M

7

Use internal clock.

CD

2

PLM

0

Use only the Preload0 register. Preload0 must be

programmed to set the pulse duration.

XC

0

External index signal.

Signal

Connect To

ClkA

NC

ClkB

GND (count down)

Index

Hardware trigger for starting an output pulse.

Leave disconnected if hardware-triggering is not

required

Output

Pulse output signal.

Field Value

Notes