Sensoray 2600 User Manual

Page 58

2600 Family Instruction Manual

53

Chapter 9 : Model 2620 Counter Module

XC: Index source:

0 - External Index pin.

1 - Internal free-running gate generator.

Response

none

Notes

After the mode is changed to its target value, the

counter core is automatically reset to zero. The

channel’s preload registers are not changed by

this action.

The target channel’s mode changes immediately

to the specified mode when the SetMode action

executes. As a result, the client may invoke

another action that will modify the counter core

(i.e., SetCounter) immediately after a

SetMode

action.

9.4.2 SetCommonControl

Function

Programs the gate time divisor and time stamp

resolution common to all counter channels.

Opcode

0x0F

Command

(Ctrl<7:0>),(Ctrl<15:8>)

Ctrl

is a 16-bit value, passed LSB first, that is

composed of two bit fields that specify the gate

time divisor (G) and time stamp resolution (TS).

These values are common to all counter channels.

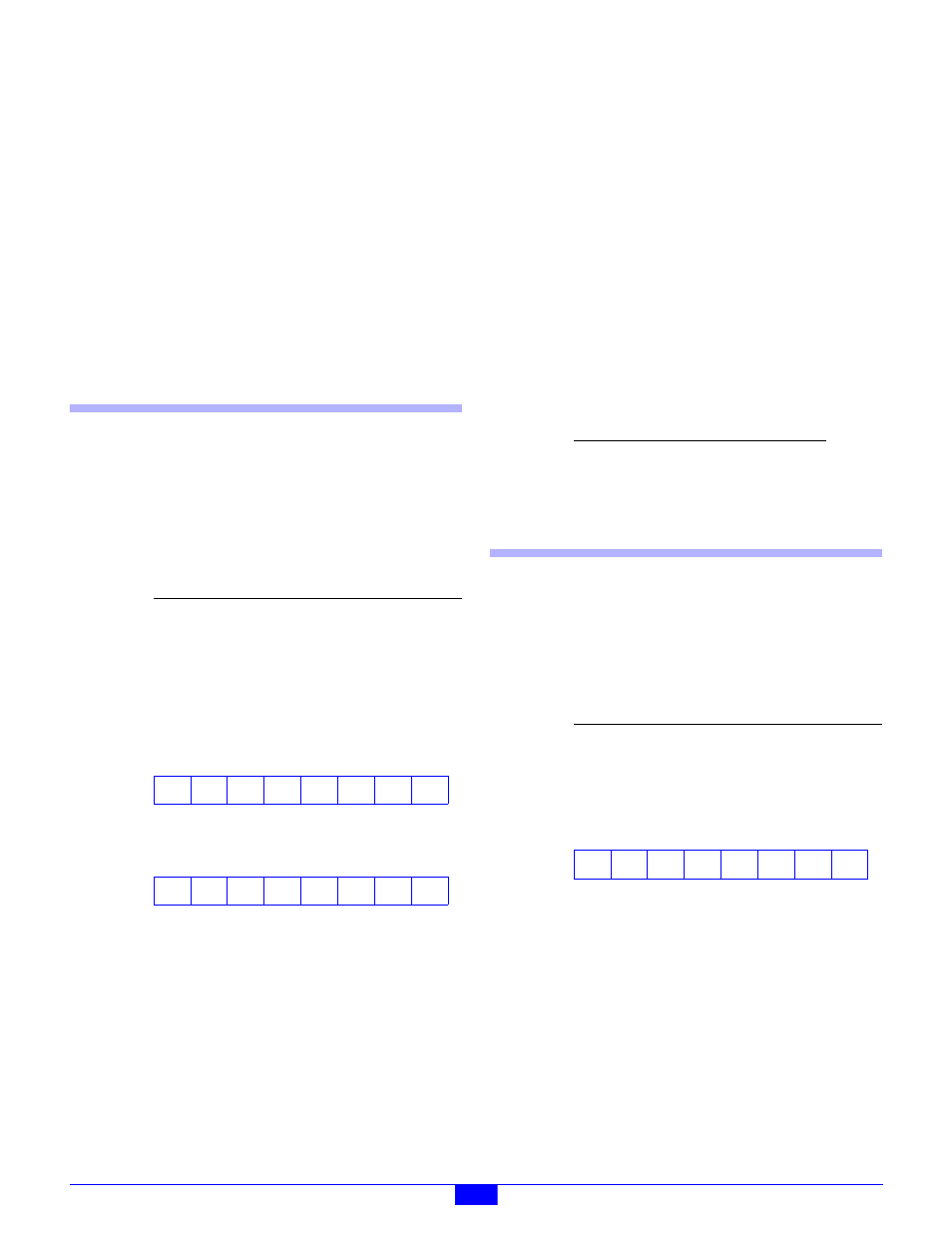

Figure 47: Ctrl MSB

Figure 48: Ctrl LSB

G: Gate time divisor (14-bit field):

2 to 16,383 - Specifies the gate time divisor

that is common to all channels. The gate

interval is set to 2*(G+1) milliseconds; this

is the period of the square-wave output

produced by the gate generator.

TS: Time stamp resolution (2-bit field):

0 - 1 microsecond.

1 - 10 microseconds.

2 - 100 microseconds.

3 - 1 millisecond.

Response

none

Notes

This action does not require a counter channel

number to be attached to the opcode byte.

When using the time gate in frequency counter

applications, set the gate time divisor so that the

gate generator period equals the desired gate

time. For example, set the gate time divisor to

499 to generate a one-second gate period.

The time stamp resolution should be programmed

so as to meet the needs of the channel having the

highest resolution; all other channels must then

use the same time stamp resolution.

The application must trade-off time stamp

resolution for longer time stamp intervals, as

shown in the following table:

9.4.3 SoftTrigger

Function

Triggers counter latch and/or load.

Opcode

0x01 + Chan * 16

Command (Flags)

Flags

contains bits that specify the action or

actions that are being triggered.

LAT: Transfer counter core to data latch.

LOD: Force counter load from a preload register.

If only one preload register is in use, Preload0 is

always used. If both preload registers are in use,

the active preload register will be used and the

register pointers will be toggled so that the other

preload register will be used next time.

Response

none

Parameter

Function

Ctrl

Common counter configuration values.

15

G13

14

G12

13

G11

12

G10

11

G9

10

G8

9

G7

8

G6

7

G5

6

G4

5

G3

4

G2

3

G1

2

G0

1

TS1

0

TS0

Resolution

Maximum Interval

1 µs

65.536 ms

10 µs

655.36 ms

100 µs

6.5536 seconds

1 ms

65.536 seconds

Parameter

Function

Flags

Bits that specify the soft trigger actions

that are being invoked.

7

0

6

0

5

0

4

0

3

0

2

0

1

LAT

0

LOD