Measurement Computing PCI-DAS6071 User Manual

Page 43

PCI-DAS6071 User's Guide

Specifications

43

Configurable AUXIN<5:0>, AUXOUT<2:0> external trigger/clocks

The PCI-DAS6071 provides nine user-configurable trigger/clock pins available at the 100-pin I/O connector. Of

these, six are configurable as inputs while three are configurable as outputs.

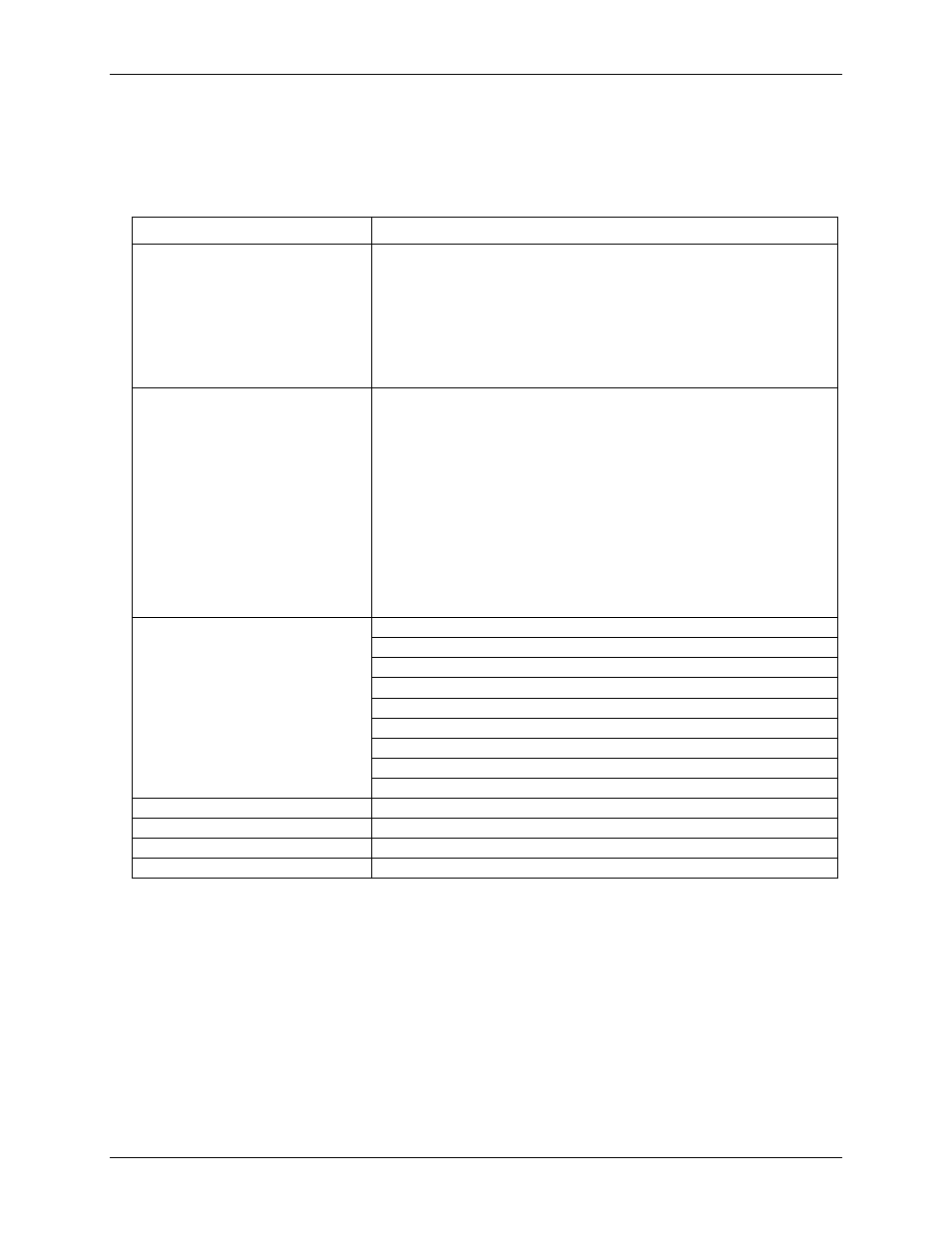

Table 21. Configurable triggers/clocks specifications

Parameter

Specification

AUXIN<5:0> sources (software

selectable)

A/D CONVERT:

External ADC convert strobe

A/D TIMEBASE IN:

External ADC pacer timebase

A/D START TRIGGER:

ADC Start Trigger

A/D STOP TRIGGER:

ADC Stop Trigger

A/D PACER GATE:

External ADC gate

D/A START TRIGGER:

DAC trigger/gate

D/A UPDATE:

DAC update strobe

D/A TIMEBASE IN:

External DAC pacer time base

AUXOUT<2:0> sources (software

selectable)

STARTSCAN:

A pulse indicating start of conversion

SSH:

Active signal that terminates at the start of the last

conversion in a scan

A/D STOP:

Indicates end of scan

A/D CONVERT:

ADC convert pulse

SCANCLK:

Delayed version of ADC convert

CTR1 CLK:

CTR1 clock source

D/A UPDATE:

D/A update pulse

CTR2 CLK:

CTR2 clock source

A/D START TRIGGER:

ADC Start Trigger Out

A/D STOP TRIGGER:

ADC Stop Trigger Out

A/D PACER GATE:

External ADC gate

D/A START TRIGGER:

DAC Start Trigger Out

Default selections:

AUXIN0:

A/D CONVERT

AUXIN1:

A/D START TRIGGER

AUXIN2:

A/D STOP TRIGGER

AUXIN3:

D/A UPDATE

AUXIN4:

D/A START TRIGGER

AUXIN5:

A/D PACER GATE

AUXOUT0:

D/A UPDATE

AUXOUT1:

A/D CONVERT

AUXOUT2:

SCANCLK

Compatibility

5 V/TTL

Edge-sensitive polarity

Rising/falling, software selectable

Level-sensitive polarity

Active high/active low, software selectable

Minimum pulse width

37.5 nS