Ctr1 gate signal, Ctr1 out signal, Ctr2 clk signal – Measurement Computing PCI-DAS6071 User Manual

Page 30

PCI-DAS6071 User's Guide

Functional Details

30

CTR1 GATE signal

You can use the CTR1 GATE signal for starting and stopping the counter, saving counter contents, etc. It is

polarity programmable and is available at the CTR1 GATE pin.

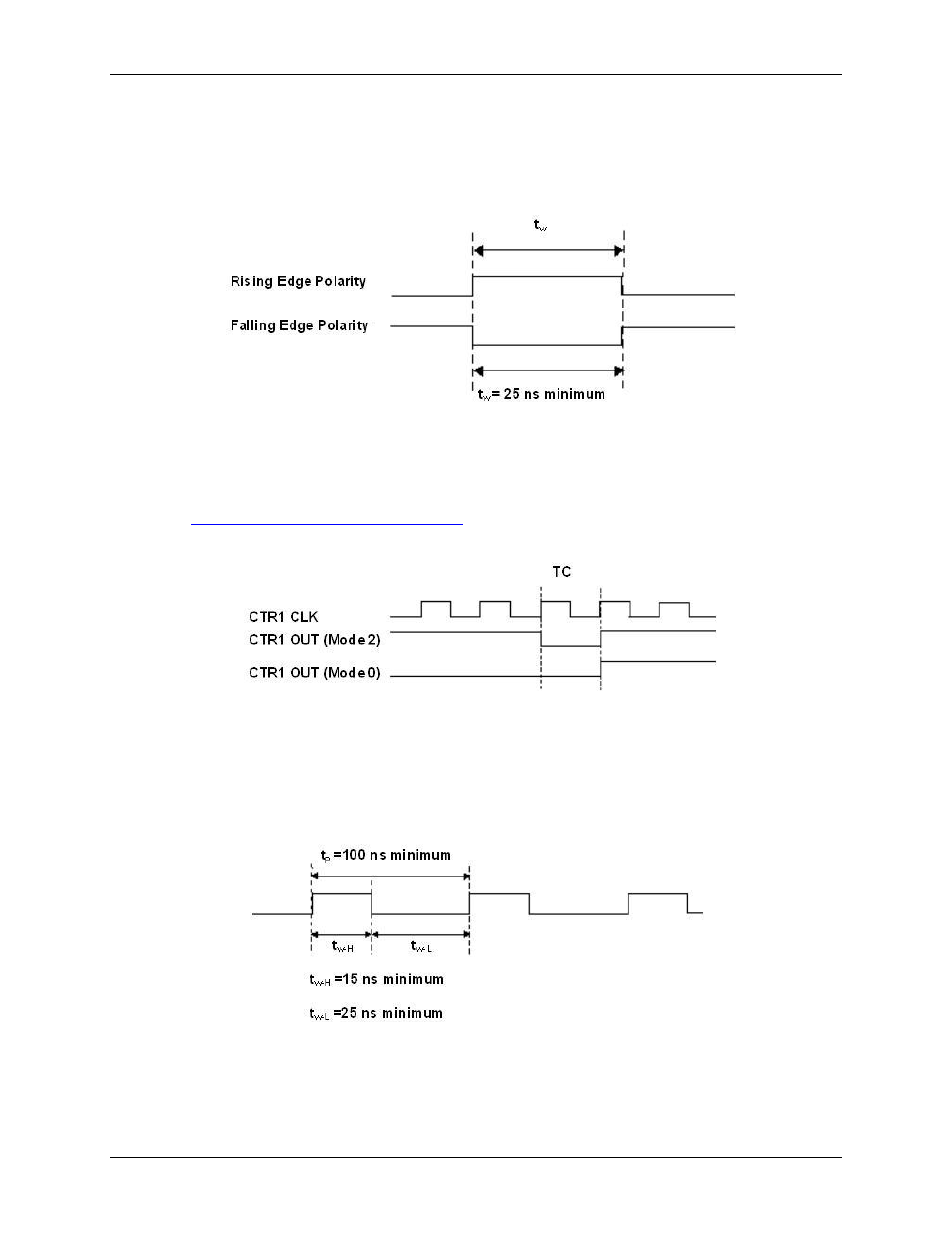

Figure 33 shows the minimum timing requirements for the CTR1 GATE signal.

Figure 33. CTR1 GATE signal timing

CTR1 OUT signal

This signal is present on the CTR1 OUT pin. The CTR1 OUT signal is the output of one of the two user’s

counters in an industry-standard 82C54 chip. For detailed information on counter operations, refer to the data

sheet a

Figure 34 shows the timing requirements for the CTR1 OUT signal for counter mode 0 and mode 2.

Figure 34. CTR1 OUT signal timing

CTR2 CLK signal

The CTR2 CLK signal can serve as the clock source for independent user counter 2. It can be selected through

software at the CTR2 CLK pin rather than using the on-board 10 MHz or 100 kHz sources. It is also polarity

programmable. The maximum input frequency is 10 MHz. There is no minimum frequency specified. Figure 35

shows the timing requirements for the CTR2 CLK signal.

Figure 35. CTR2 CLK signal timing