1 post routines, Table 5-6, Post routines – Artesyn ATCA-F120 Installation and Use (August 2014) User Manual

Page 99: U-boot firmware

U-Boot Firmware

ATCA-F120 Installation and Use (6806800D06J)

99

5.8.1

POST Routines

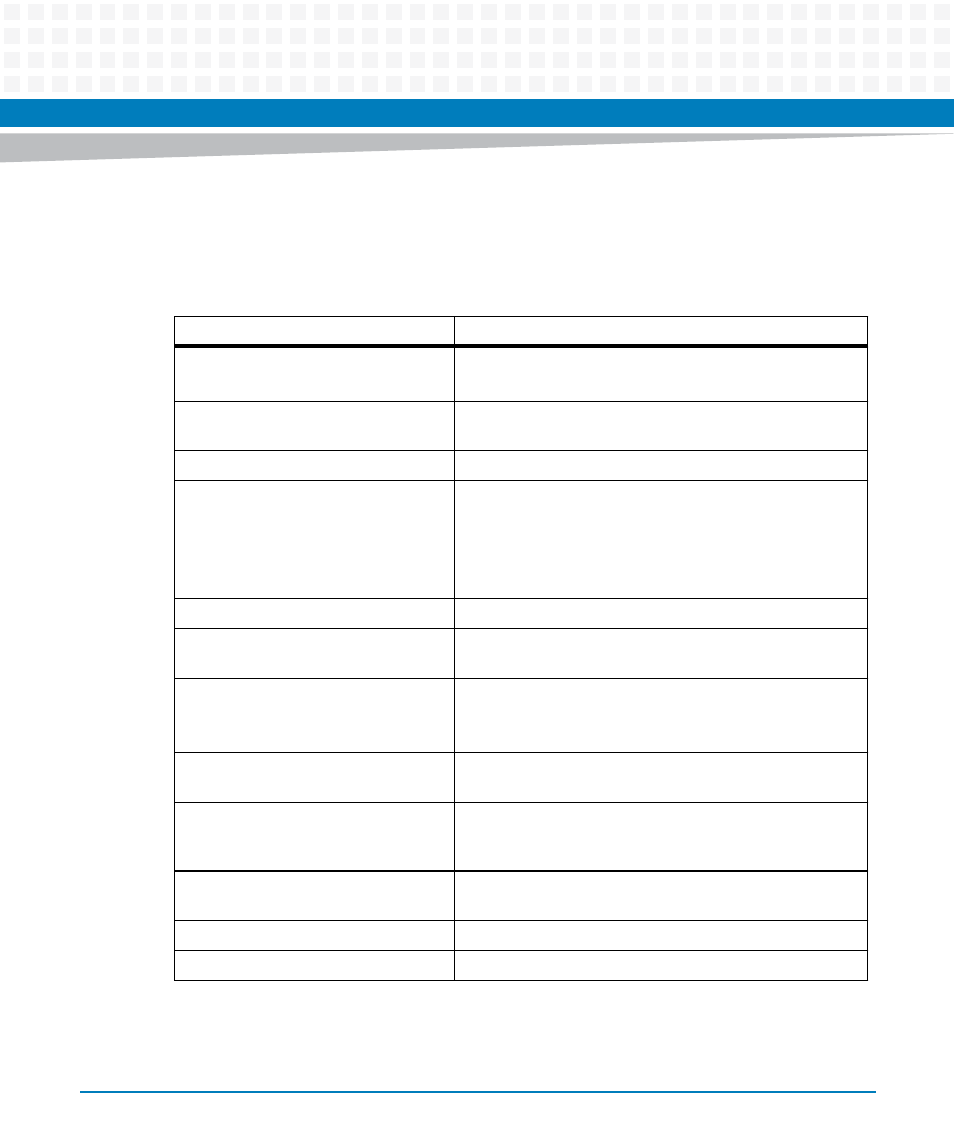

The following table describes in detail which POST routines are performed.

Table 5-6 POST Routines

Device

Description

CPU

Check PLL configuration (PORPLLSR register).

Check device configuration (PORDEVSR register)

FPGA

Register sanity check. The version code is checked. It must

not be 0x00 or 0xFF.

DRAM

Address line and data-line test.

Switch devices

The PCI interface is checked as follows:

Check for configuration space access (vendor/device

ID)

Perform walking-one test on first memory-mapped

register

Base interface extender/SPI

Data test on LED register page 0, offset 0x12

I2C buses

Check whether bus addresses 0x31, 0x44, 0x46, 0x47,

0x50, 0x51 are accessible on bus 0 and 0x50, 0x70 on bus 1.

RTC

Checks whether the second counter is advancing.

Compares the number of CPU ticks in one second against

the expected system clock frequency (66 MHz)

MDIO/PHY

Attempts to read model and device ID from PHY address 0..

3

TSEC network port

The PHY for each TSEC port is configured to loop back

mode, 100 and 1000 MBPS, and 10000 loop back packets

are sent and verified.

Boot flash

Flash devices are sent into CFI query mode and the query

string is verified.

User (NAND) flash

Check connectivity of NAND flash devices.

RTM

Check connectivity of 10G repeater devices on RTM