Comunicación de estado – AMETEK XDL Series II User Manual

Page 174

173

*PRE

bytes de estado con un operador lógico AND; si el resultado es 0, el valor de

ist

será 0, de lo

contrario el valor de

ist

será 1.

El instrumento también debe configurarse de manera que, durante una operación de sondeo, se

pueda devolver al controlador el valor de

ist

. Para ello, el controlador envía un comando Parallel

Poll Configure (PPC) seguido de un comando Parallel Poll Enable (PPE). A continuación se

muestran los bits del comando PPE:

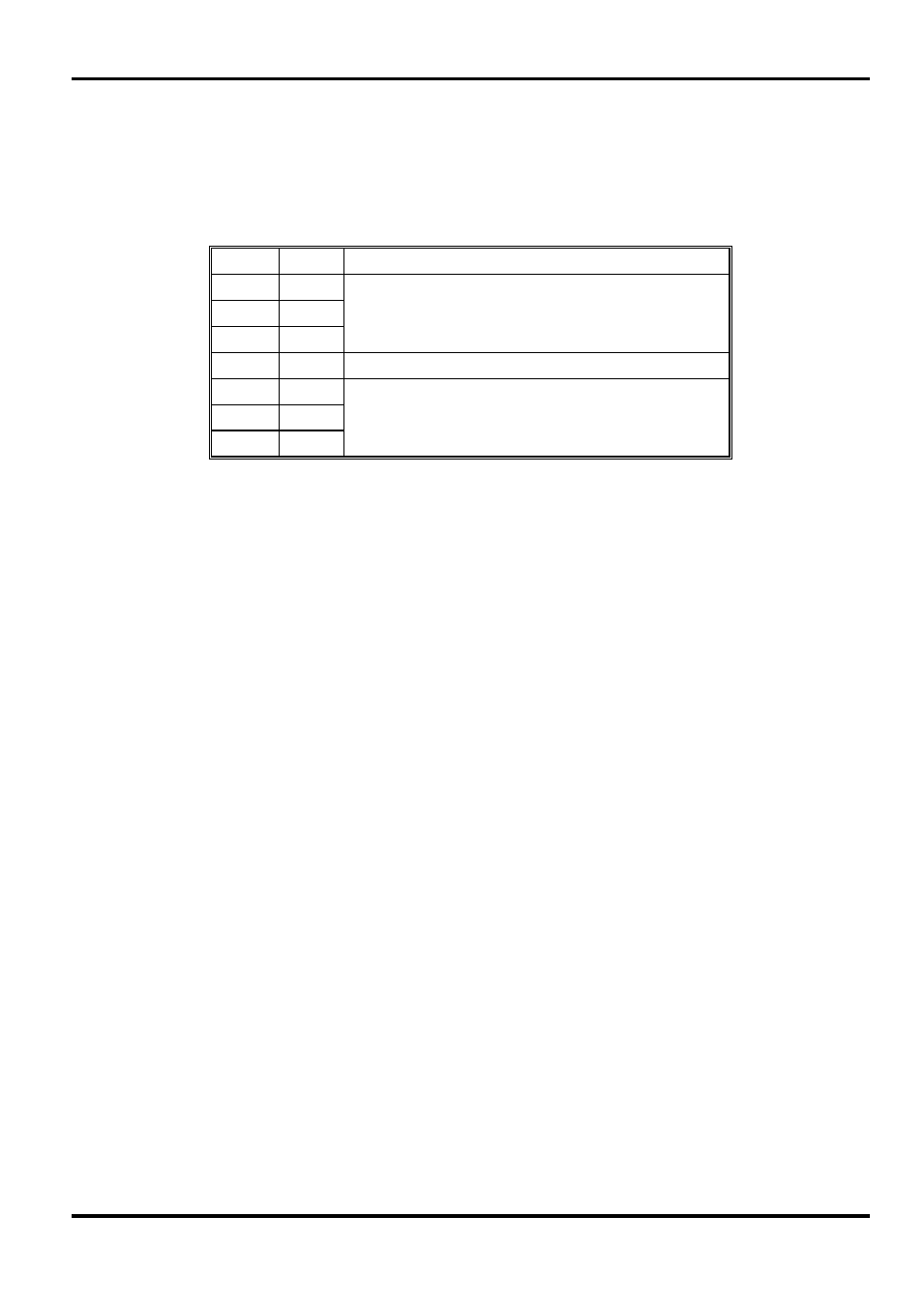

bit 7 =

X

indiferente

bit 6 =

1

bit 5 =

1

Sondeo en paralelo habilitado

bit 4 =

0

bit 3 = Sentido sentido del bit de respuesta; 0 = bajo, 1 = alto

bit 2 =

?

bit 1 =

?

posición de bit de la respuesta

bit 0 =

?

Para devolver el bit RQS (bit 6 del Status Byte Register), con valor 1 cuando sea verdadero

y con valor 0 cuando sea falso, en la posición de bits 1, en respuesta a una operación de

sondeo en paralelo, envíe los siguientes comandos:

*PRE 64

, después PPC seguido de 69H (PPE)

La respuesta del aparato al sondeo será entonces 00H si RQS es 0 y 01H si RQS es 1.

Durante la respuesta a un sondeo de este tipo, las líneas de la interfaz DIO se encuentran

terminadas resistivamente (terminación pasiva). Ello permite a múltiples dispositivos compartir la

misma posición de bits para la respuesta, tanto en la configuración wired-AND como en la

configuración wired-OR. Consulte la norma IEEE 488.1 para más información.

Comunicación de estado

En esta sección se describe el modelo de estado completo del instrumento. Tenga en cuenta que

algunos registros son específicos de la sección GPIB del instrumento y son de uso limitado en un

entorno RS232.

Registro de estado de eventos estándar y registro de activación de estado de eventos estándar

Ambos registros se implementan conforme a lo especificado por la norma IEEE 488.2.

Todo bit activado en el Standard Event Status Register que se corresponda con un bit activado

en el Standard Event Status Enable Register provocará la activación del bit ESB en el Status

Byte Register.

El Standard Event Status Register se lee y borra con el comando *ESR?. El Standard Event Status

Enable Register se configura con el comando *ESE

Bit 7 - Power On (encendido). Se configura cuando se enciende por primera vez el instrumento.

bit 6 - No se usa.

bit 5 - Command Error (error de comando). Se activa cuando se detecta un error de sintaxis en

un comando procedente del bus. El analizador se reinicia y el análisis continúa en el

siguiente byte del flujo de entrada.

bit 4 - Execution Error (error de ejecución). Se configura cuando se descubre un error mientras

se intenta ejecutar un comando ya completamente analizado sintácticamente. En el

Execution Error Register aparecerá el número de error correspondiente.

De 1 a 99

Indica que se ha detectado un error de hardware.

116

Se ha solicitado una recuperación de datos de configuración, pero la

memoria especificada no contiene ningún dato.