Interrogazione ciclica in parallelo gpib – AMETEK XDL Series II User Manual

Page 138

137

Controller

C0

Interfaccia elettrica

E2

Gestione degli errori GPIB a norma IEEE 488.2 - Registro errori richieste di informazioni

L'errore IEEE 488.2

UNTERMINATED

(invito al dialogo senza dati da inviare) viene gestito nel modo

seguente. L'errore UNTERMINATED viene generato quando lo strumento è invitato a dialogare

con il codice di formattazione risposta inattivo e la coda dati d'ingresso vuota. Questo comporta

l'impostazione di un Query Error (errore di domanda) nello Standard Event Status Register

(registro andamento eventi ordinari), l'inserimento del valore 3 nel registro del Query Error e il

ripristino dell’analizzatore sintattico. Per ulteriori ragguagli, vedere la sezione Rapporti di stato.

L'errore IEEE 488.2

INTERRUPTED

(interruzione) viene gestito nel modo seguente. Se il codice di

formattazione risposte è in attesa d'inviare un messaggio di risposta e l’analizzatore sintattico

legge il codice

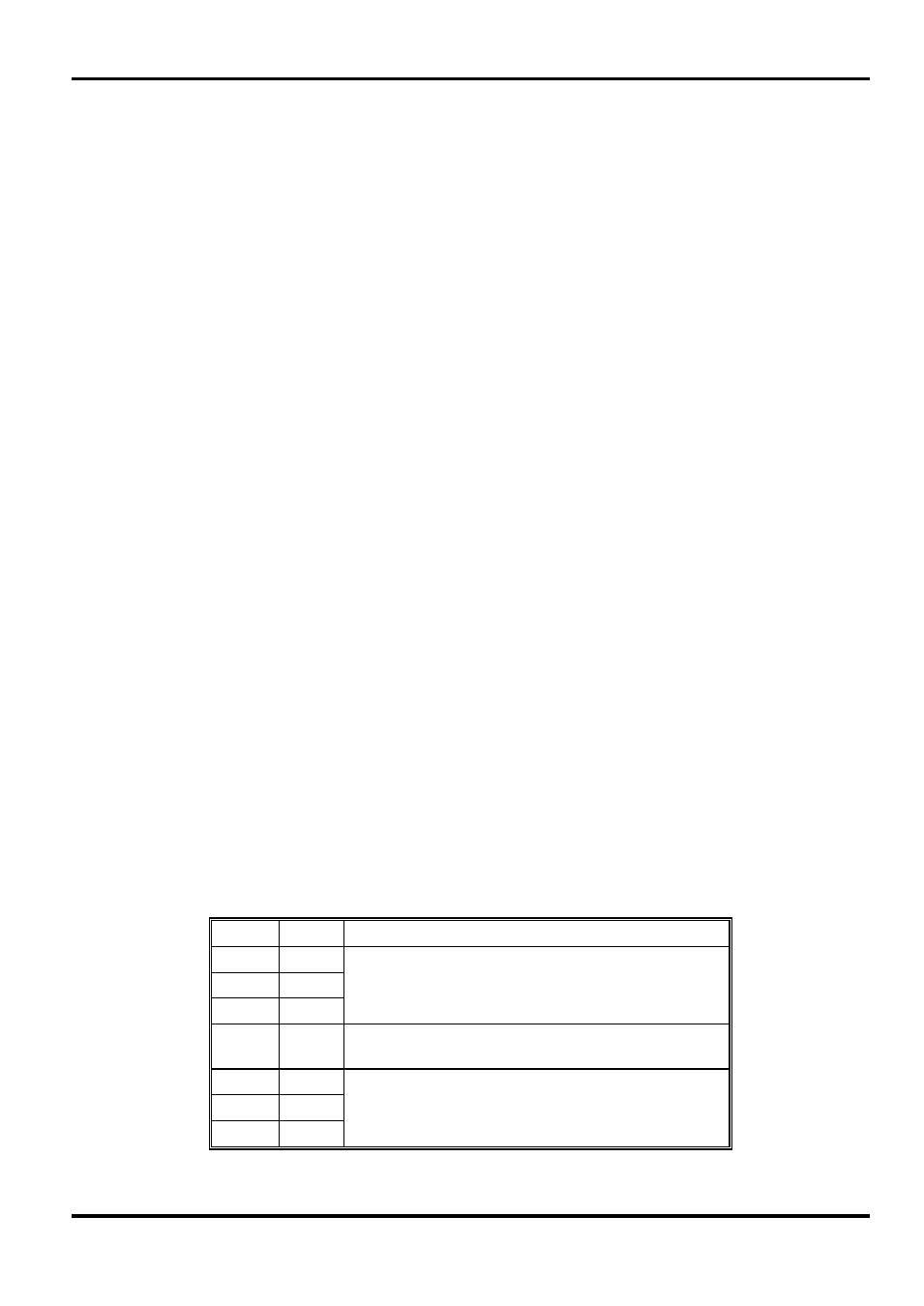

> (codice finale messaggio programma) o la coda dei messaggi in entrata contiene più di un messaggio END (fine), lo strumento riceve il codice INTERRUPTED e viene generato un errore. Questo comporta l'impostazione di un bit Query Error nello Standard Event Status Register, l'inserimento del valore 1 nel Query Error Register e il > (elemento di messaggio del programma) dalla coda dei dati in entrata. Per ulteriori ragguagli, L'errore IEEE 488.2 DEADLOCK (blocco dati) viene gestito nel modo seguente. Qualora il codice di formattazione risposte sia in attesa di inviare un messaggio di risposta e la coda dei dati in DEADLOCK e viene generato un errore. Questo comporta l'impostazione di un bit Query Error nello Standard Event Status Register, l'inserimento > (elemento di messaggio del programma) dalla coda dei dati in entrata. Per ulteriori ragguagli, vedere la sezione Rapporti di stato. Interrogazione ciclica in parallelo GPIB Lo strumento è dotato di tutte le funzioni di interrogazione ciclica in parallelo. Il Parallel Poll ist . Il Parallel Poll Enable Register viene impostato dal comando *PRE ist è 0, altrimenti il valore di ist è 1. Lo strumento deve anche essere configurato di modo che il valore di ist possa essere restituito al controller durante l’operazione d’interrogazione ciclica parallela. Il controller configura lo bit 7 = X privo di significato bit 6 = 1 bit 5 = 1 abilitazione dell’interrogazione ciclica parallela bit 4 = 0 bit 3 = Significa to significato della risposta bit; 0 = basso, 1 = alto bit 2 = ? bit 1 = ? posizione bit della risposta bit 0 = ?

ripristino del codice di formattazione risposte, che svuota la coda dei dati in uscita. L’analizzatore

sintattico inizierà poi ad analizzare la sintassi della successiva

vedere la sezione Rapporti di stato.

entrata sia piena, lo strumento entra nella modalità

del valore 2 nel Query Error Register e il ripristino del codice di formattazione risposte, che svuota

la coda dei dati in uscita. L’analizzatore sintattico inizierà poi ad analizzare la sintassi della

successiva

Enable Register viene impostato per indicare quali bit nello Status Byte Register (registro stato

byte) occorre utilizzare per formulare il messaggio locale

Register viene aggiunto allo Status Byte Register in configurazione AND; se il risultato è zero, il

valore di

strumento inviando il comando Parallel Poll Configure (PPC) (configura interrogazione ciclica

parallela) seguito dal comando Parallel Poll Enable (PPE) (abilita interrogazione ciclica). I bit nel

comando PPE sono riportati di seguito: