Altera SerialLite II Protocol User Manual

Page 59

Altera Corporation

59

SerialLite II Protocol Reference Manual

SerialLite II Specification

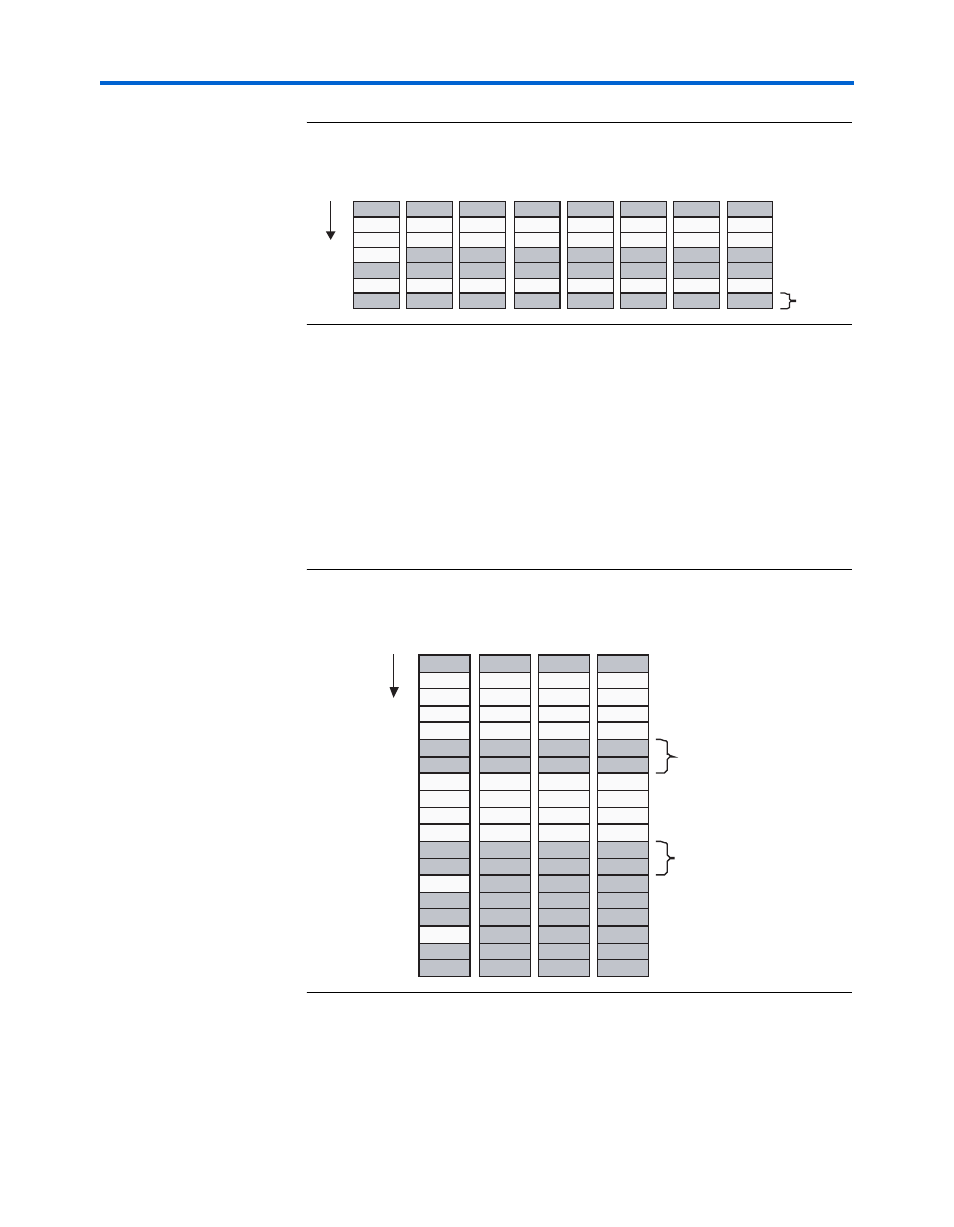

Figure 2–37. CRC Alignment for Eight Lanes

Breaking data packets is treated like the end-of-packet as the CRC is

appended to the two byte SUP sequence. The CRC is calculated over that

burst of user data. When the packet is resumed, the initial value used is

the all ones pattern as described below. This allows burst transfers to be

verified before the end-of-packet. As the CRC is computed on each burst

instead of the entire packet, saving of context is not required and the CRC

remainder is discarded making implementation simpler. Having the CRC

computed only over the burst is advantageous for systems using large

packet sizes or susceptible to high bit error rates.

Figure 2–38. SUP Sequence followed by CRC

Time

D8

IDL

D 12

D 16

PD0

PD4

D0

D4

D9

IDL

D 13

PD1

PD5

D1

D5

D 10

D 14

PD2

PD6

D2

D6

D 11

D 15

PD3

PD7

D3

D7

CRC1

CRC2

CRC3

CRC4

EG P1

EG P2

SPP1

SPP2

IDL

EG P1

IDL

EG P2

SDP1

IDL

SDP2

IDL

IDL

IDL

IDL

IDL

IDL

Lane

# 0

Lane

# 1

Lane

# 2

Lane

# 3

Lane

# 4

Lane

# 5

Lane

# 6

Lane

# 7

IDL

IDL

IDL

IDL

IDL

IDL

IDL

IDL

CRC-32

D8

IDL

D 12

D0

D4

D9

IDL

D 13

D1

D5

D 10

SDP1

D 14

D2

D6

D 11

0 0

D 15

D3

D7

D8

SUP1

D 12

D0

D4

D9

0 0

D 13

D1

D5

D 10

SDP1

D 14

D2

D6

D 11

0 1

D 15

D3

D7

SUP1

0 1

CDP1

0 0

D 16

IDL

IDL

IDL

EG P1

0 0

CDP1

0 1

D 16

IDL

IDL

IDL

EG P1

0 1

IDL

IDL

Lane

# 0

Lane

# 1

Lane

# 2

Lane

# 3

CRC1

CRC2

CRC3

CRC4

CRC1

CRC2

CRC3

CRC4

CRC1

CRC2

CRC3

CRC4

CRC1

CRC2

CRC3

CRC4

Time

Suspended packet

followed by CRC-32

Suspended packet

followed by CRC-32