Reset state, Character alignment state – Altera SerialLite II Protocol User Manual

Page 33

Altera Corporation

33

SerialLite II Protocol Reference Manual

SerialLite II Specification

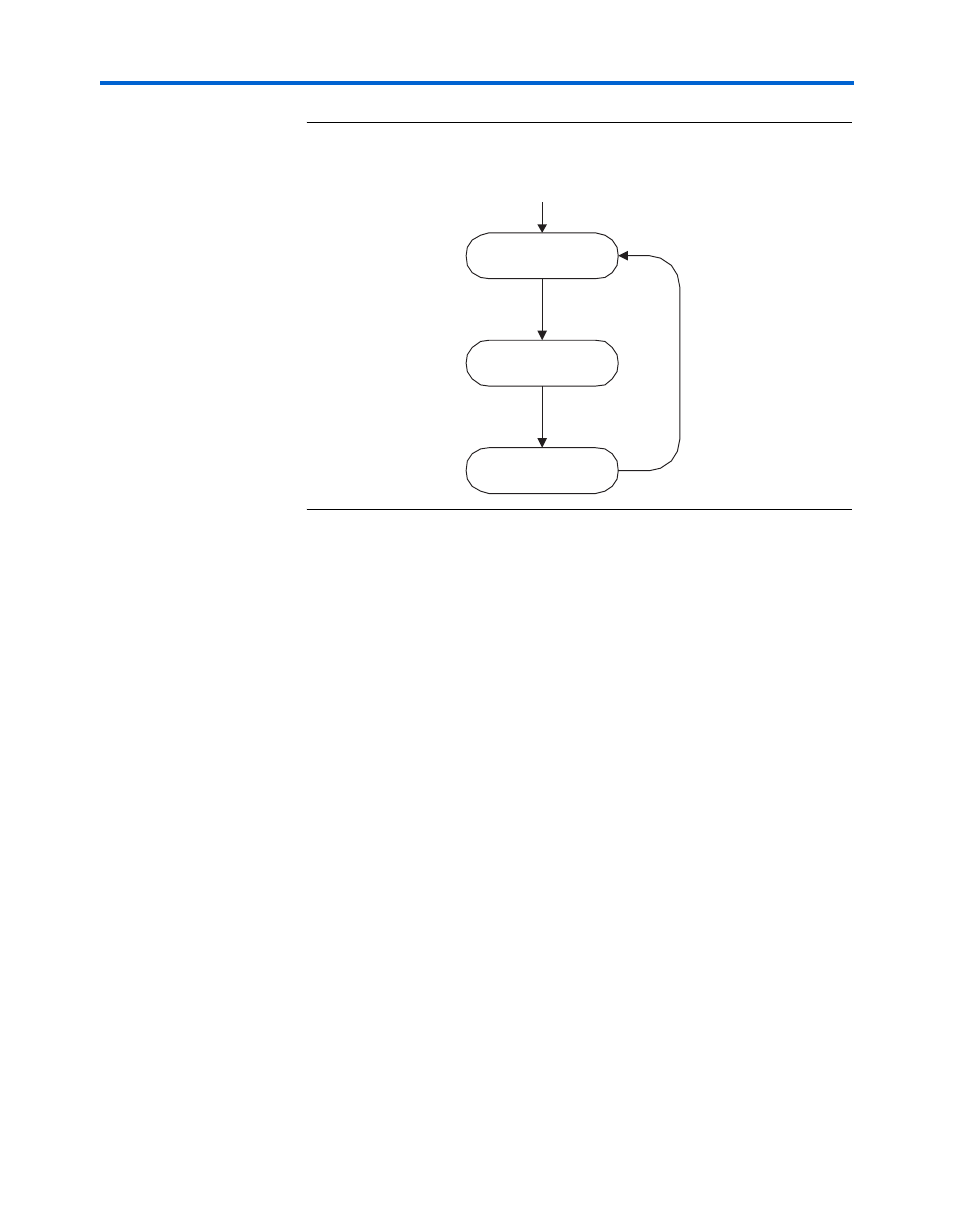

Figure 2–14. Self Synchronizing Link Training State Machine

Reset State

The reset state is the first state of the lane initialization state machine. It

can be entered at any time by a power-on reset, hardware reset, or link

error. The transmitter is disabled and its outputs are driven into a

quiescent state (zero-volt differential). The received is initialized.

The receiver discards all received data and flushes any data in progress.

All state machines and registers are set to their initialization values. All

counters, timers, pointers, and expected segment ID for transmission of

priority packets are reset. The link-up status is cleared to indicate the link

is down.

After reset is complete, the receiver/transmitter transitions to the

character alignment state.

Character Alignment State

In this state, bit lock and symbol alignment is achieved. The

implementation of the transmitter initialization sequence is user defined.

1

Channel alignment will be defined in a future version of

this specification.

Once at least 64 valid characters are received on each lane, the receiver

transitions to the link-up state. Valid characters can be any special

character or data character.

Reset

Link-Up

Pow er-On Reset

or Hardw are Reset

Character Alignment

Link Error