Transfer size, Figure 2–31. illegal multi-lane alignment – Altera SerialLite II Protocol User Manual

Page 52

52

Altera Corporation

SerialLite II Protocol Reference Manual

Data Link Layer Description

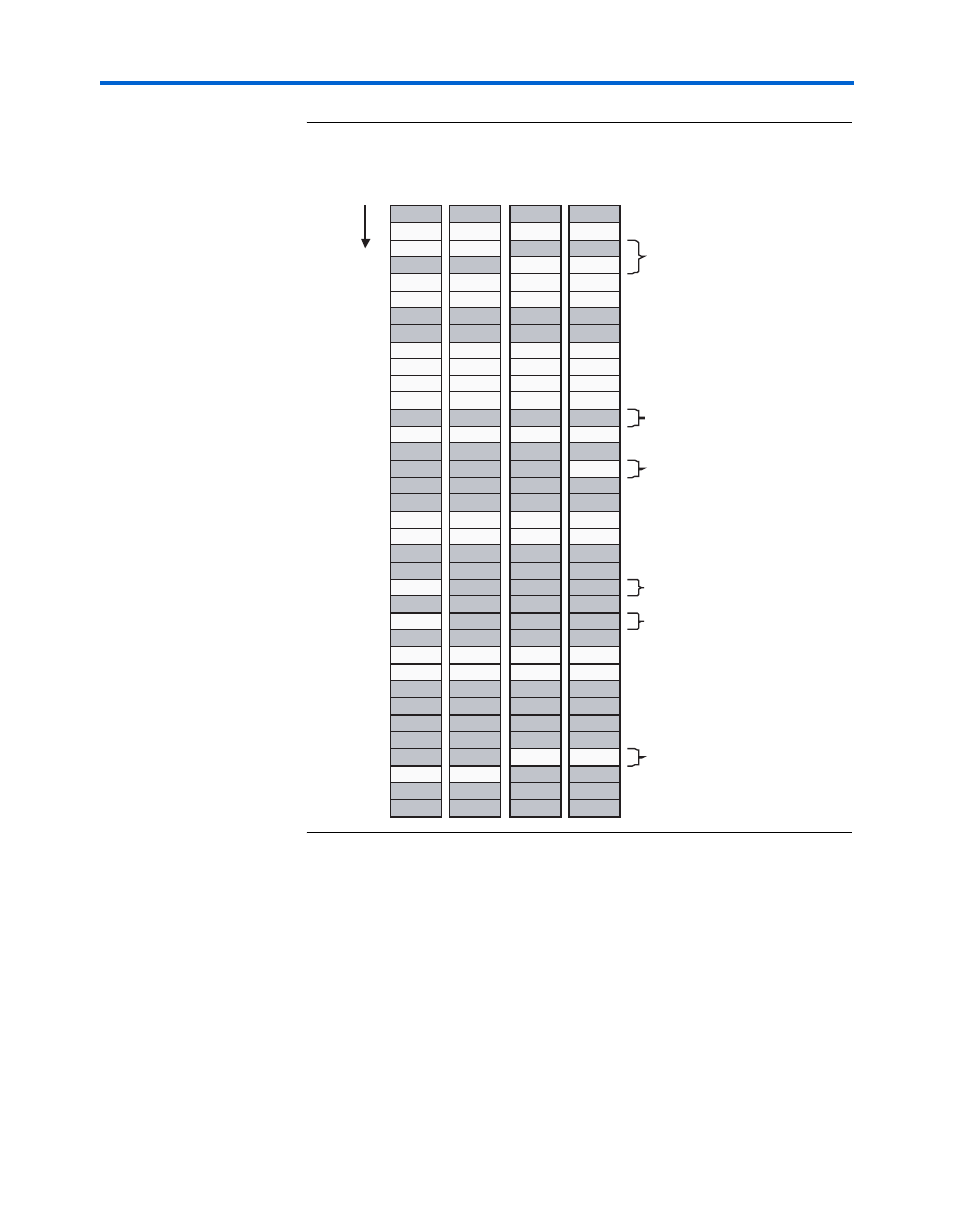

Figure 2–31. Illegal Multi-Lane Alignment

Transfer Size

The concept of sending data in bursts is used to support high data rates

with a minimal amount of resources. A parameter called transfer size

defines the granularity of the data burst. Data transfers are required to be

sent contiguously until the end-of-packet or a multiple of the transfer

size. Shorter packets are padded with idle characters until a multiple of

the transfer size is reached. Control sequences, such as the clock

compensation sequence and link management packets, should not

interrupt the data transfer until the next multiple of the transfer size. Any

number of control characters can be sent between data transfers.

Time

SLP

LD 0

LD 1

LD 2

Illegal: CRC must follow end-of-

packet.

IDL

IDL

IDL

IDL

Illegal: Link Mgmt packet

cannot occupy same column

as Data packet

D8

IDL

D 12

D0

D4

D9

IDL

D 13

D1

D5

D 10

SDP1

D 14

D2

D6

D 11

0 0

D 15

D3

D7

D8

D 12

D0

D4

D9

D 13

D1

D5

D 10

D2

D6

D 11

D3

D7

SUP1

0 1

CDP1

0 0

D 16

IDL

0 0

CDP1

0 1

D 16

IDL

EG P1

Lane

# 0

Lane

# 1

Lane

# 2

Lane

# 3

CRC1

CRC2

PD0

PD4

EG P1

PD1

PD5

0 0

PD2

PD6

IDL

PD3

PD7

IDL

CRC1

CRC2

CRC3

CRC4

SPP1

0 0

IDL

IDL

CRC1

CRC2

Illegal: End-of-packet must be

aligned on Lane 0

Illegal: Break data packet is

missing CRC bytes.

IDL

IDL

D 17

D 18

D 19

D 20

PD0

PD4

EG P1

PD1

PD5

1 0

PD2

PD6

IDL

PD3

PD7

IDL

CRC1

CRC2

CRC3

CRC4

SPP1

1 0

EG P1

0 1

IDL

D0

IDL

D1

SDP1

D2

0 0

D3

EG P1

0 0

CRC1

CRC2

IDL

IDL

IDL

IDL

IDL

IDL

IDL

IDL

SLP

LD 0

LD 1

LD 2

Illegal: Start-of-packet must be

aligned to Lane 2

SLP

LD 0

LD 1

LD 2

D 14

D 15

D 21

IDL

Illegal: Idles within a packet

must occupy an entire column

or pad end-of-packet

SUP1

0 0

SDP1

0 1

CRC1

CRC2

IDL

IDL