Altera Arria GX Development Board User Manual

Page 35

Altera Corporation

Reference Manual

2–25

October 2007

Arria GX Development Board

Board Components

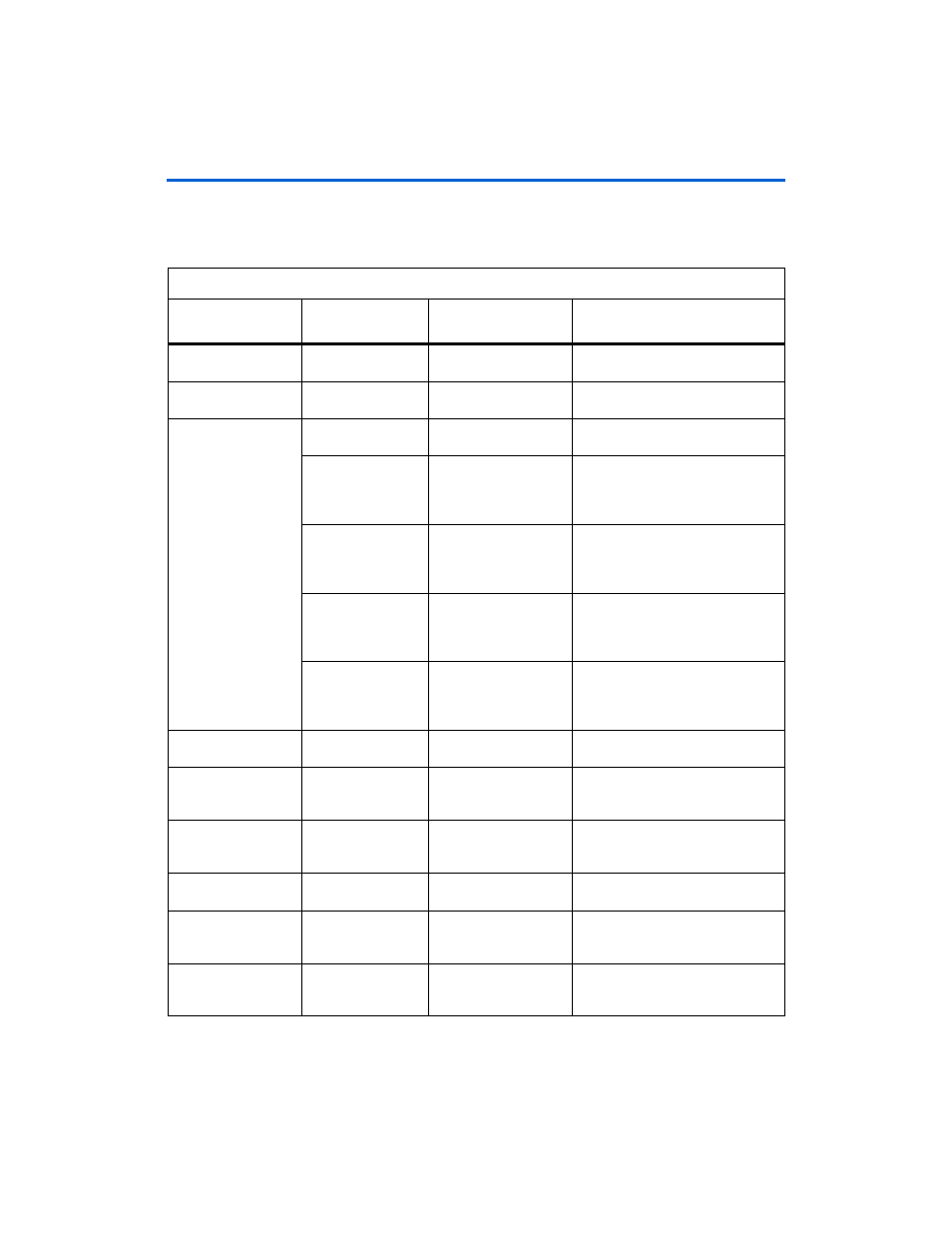

Table 2–24

lists HSMC interface pin-out as well as corresponding

Arria GX device pin numbers.

Table 2–24. HSMC Interface Pin-Out (Part 1 of 2)

Description

Type

Schematic

Signal Name

Arria GX Device

Pin Number

Transceiver transmit

channels

1.5 V PCML

(4 TX channels)

HSMA_TX_P(3:0)

HSMA_TX_N(3:0)

N4, L4, C4, E4

N5, L5, C5, E5

Transceiver receive

channels

1.5 V PCML

(4 RX channels)

HSMA_RX_P(3:0)

HSMA_RX_N(3:0)

N1, L1, E1, G1

N2, L2, E2, G2

Data bus

2.5 V LVCMOS in/out

(4 bits)

HSMA_D(3:0)

A24, A23, A26, A25

2.5 V LVCMOS in/out

(17 bits)

or LVDS

(17 TX channels-p)

HSMA_TX_D_P(16:0)

F24, E26, G24, H23, K24, G26, H26,

J25, K26, M25, P25, Y25, AA26,

AA23, AB22, AB24, AC25

2.5 V LVCMOS in/out

(17 bits)

or LVDS

(17 TX channels-n)

HSMA_TX_D_N(16:0)

F23, E25, G23, H22, J23, G25, H25,

J24, K25, M24, P24, Y24, AA25,

AA22, AB21, AB23, AC24

2.5 V LVCMOS in/out

(17 bits)

or LVDS

(17 RX channels-p)

HSMA_RX_D_P(16:0)

C28, D28, E28, F27, G28, H28, L28,

N28, R28, V28, Y28, Y27, AB28,

AC28, AC27, AE28, AF28

2.5 V LVCMOS in/out

(17 bits)

or LVDS

(17 RX channels-n)

HSMA_RX_D_N(16:0)

C27, D27, F28, F26, G27, J28, M28,

P28, T28, W28, AA28, Y26, AB27,

AD28, AC26, AE27, AF27

Clock output 0

2.5 V LVCMOS clock

output

HSMA_CLKOUT0

A15

Clock output 1

2.5 V LVCMOS in/out

(2 bits)

or LVDS clock out

HSMA_CLKOUT_P1

HSMA_CLKOUT_N1

AC23

AC22

Clock output 2

2.5 V LVCMOS in/out

(2 bits)

or LVDS clock out

HSMA_CLKOUT_P2

HSMA_CLKOUT_N2

AE26

AE25

Clock input 0

2.5 V LVCMOS clock

in

HSMA_CLKIN0

T25

Clock input 1

2.5 V LVCMOS in/out

(2 bits)

or LVDS clock in

HSMA_CLKIN_P1

HSMA_CLKIN_N1

U26

U25

Clock input 2

2.5 V LVCMOS in/out

(2 bits)

or LVDS clock in

HSMA_CLKIN_P2

HSMA_CLKIN_N2

R26

R25