Standard communication ports, Pci express edge connector interface (j14), Standard communication ports -23 – Altera Arria GX Development Board User Manual

Page 33: Pci express edge connector interface (j14) -23

Altera Corporation

Reference Manual

2–23

October 2007

Arria GX Development Board

Board Components

Standard

Communication

Ports

The board supports the following communication ports discussed in this

section:

■

PCIe edge connector interface

■

High-speed Mezzazine card interface

■

JTAG interface

PCI Express Edge Connector Interface (J14)

The board features a x4 (four channel) PCIe edge connector, which

operates at 2.5 Gb/s nominal rate using the FPGA transceivers from one

transceiver block.

1

The PCIe mode select jumper (J13) indicates—to the host

controlling the Arria GX development board—whether the card

is operating in PCIe x1 or PCIe x4 mode. The J13 jumper is

necessary because in some systems the prsnt pins are the only

PCIe interface indicators of supported bus width of the installed

card. Some computers may require that the jumper be installed

to operate in the PCIe x1 mode.

The PCIe signals have differential traces terminated on the receive-side

using internal termination resistors in the Arria GX device receiver pins.

Table 2–22

lists the PCIe edge connector pin-out, descriptions, and signal

type. Signal directions are relative to the Arria GX device..

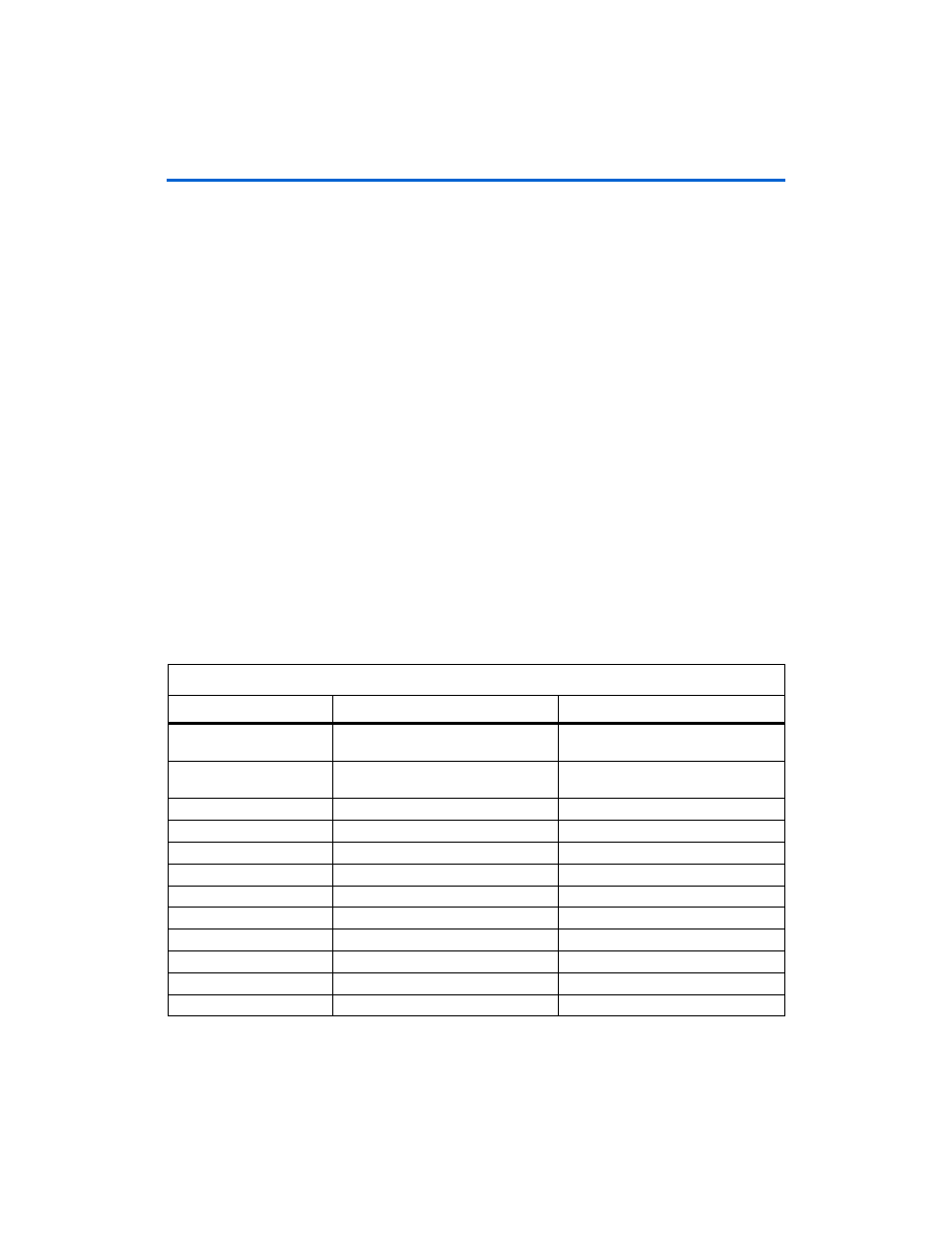

Table 2–22. PCIe Edge Connector Pin-Out (Part 1 of 2)

Schematic Signal Name

Description

Signal Type

PCIE_TX_P(3:0)

PCIE_TX_N(3:0)

Transmitter differential pairs

1.2 V PCML (4 TX channels)

PCIE_RX_P(3:0)

PCIE_RX_N(3:0)

Receiver differential pairs

1.2 V PCML (4 RX channels)

PCIE_PRSNT2n_X1

Hot plug present detect 1

N/A (jumper to

PCIE_PRSNT1n

)

PCIE_PRSNT2n_X4

Hot plug present detect 1

N/A (jumper to

PCIE_PRSNT1n

)

PCIE_SMBCLK

SMBus clock (optional)

LVTTL out (open-drain)

PCIE_SMBDAT

SMBus data (optional)

LVTTL in/out (open-drain)

TRST#

JTAG reset (optional)

N/A

TCK

JTAG clock (optional)

N/A

TDI

JTAG data in (optional)

N/A

TDO

JTAG data out (optional)

N/A

TMS

JTAG test mode select (optional)

N/A

PCIE_WAKEn

Link reactivation signal

LVTTL out (isolate with a jumper)