Fpga programming over external usb-blaster, Fpga programming over external usb-blaster –17 – Altera DSP Development Kit, Stratix V Edition User Manual

Page 25

Chapter 2: Board Components

2–17

Configuration, Status, and Setup Elements

July 2012

Altera Corporation

DSP Development Kit, Stratix V Edition

Reference Manual

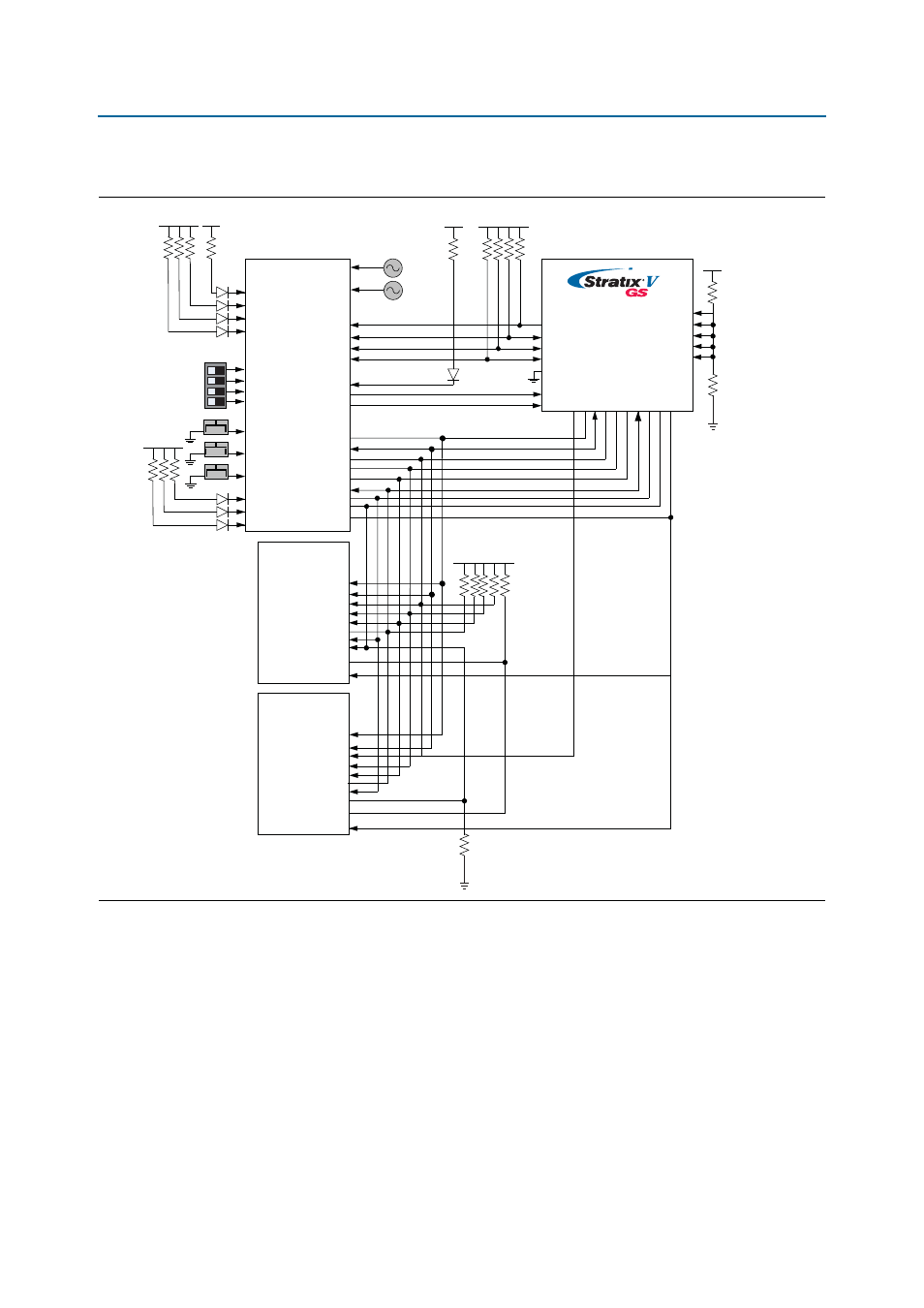

shows the PFL configuration.

f

For more information on the flash memory map storage, refer to

.

FPGA Programming over External USB-Blaster

The JTAG programming header provides another method for configuring the FPGA

(U15) using an external USB-Blaster device with the Quartus II Programmer running

on a PC. The external USB-Blaster connects to the board through the JTAG header

(J10).

Figure 2–4. PFL Configuration

MAX V CPLD

System Controller

FPGA_DATA [0]

FPGA_DCLK

FLASH_A [25:1]

FLASH_D [31:0]

DATA [0]

DCLK

INIT_DONE

nSTATUS

nCONFIG

CONF_DONE

MSEL0

MSEL1

MSEL2

MSEL3

2.5 V

10 k

Ω

nCE

CFI Flash

CONF_DONE LED

1 k

Ω

FLASH_CEn

FLASH_OEn

FLASH_WEn

FLASH_A [25:0]

FLASH_D [15:0]

FLASH_CEn

FLASH_OEn

FLASH_WEn

FLASH_WPn

FLASH_ADVn

FLASH_ADVn

FPGA_nCONFIG

FPGA_CONF_DONE

FM Bus Interface

FLASH_RYBSYn

FPGA_nSTATUS

ERROR

LOAD

FACTORY

USB-BLASTER

1.8 V

10 k

Ω

2.5 V

FLASH_RYBSYn

PGM_SEL

CONF_DONE

2.5 V

10 k

Ω

FLASH_CLK

FLASH_CLK

FLASH_RSTn

FLASH_RESETn

50 MHz

100 MHz

PGM_CONFIG

MAX_RESETn

56.2

Ω

2.5 V

1 k

Ω

MSEL4

MSEL[4:0] also

connects to MAX V

FPGA_INIT_DONE

2.5 V

56.2

Ω

CLK_SEL

CLK_ENABLE

USER_PGM

USB_SELECT

DIP Switch

PGM_LED0

PGM_LED1

PGM_LED2

2.5 V

56.2

Ω

CFI Flash

FLASH_A [25:0]

FLASH_D [15:0]

FLASH_CEn

FLASH_OEn

FLASH_WEn

FLASH_WPn

FLASH_ADVn

FLASH_RYBSYn

FLASH_CLK

FLASH_RESETn

10 k

Ω