Table 3–13 – Altera HyperTransport MegaCore Function User Manual

Page 58

3–32

Chapter 3: Specifications

HyperTransport MegaCore Function Specification

HyperTransport MegaCore Function User Guide

© November 2009

Altera Corporation

Preliminary

shows the format of the primary interface capabilities block. The block is

located at the address specified in the Capabilities Pointer field in the CSR map shown

in

The following sections explain the entries in

HT Device Header

The following sections describe the HT device header.

Vendor ID, Device ID (Offset 0x00)

Vendor ID and device ID are read-only, as defined in the PCI specification. They are

parameters in the HyperTransport MegaCore function.

PCI Command Register (Offset 0x04)

describes the PCI command register.

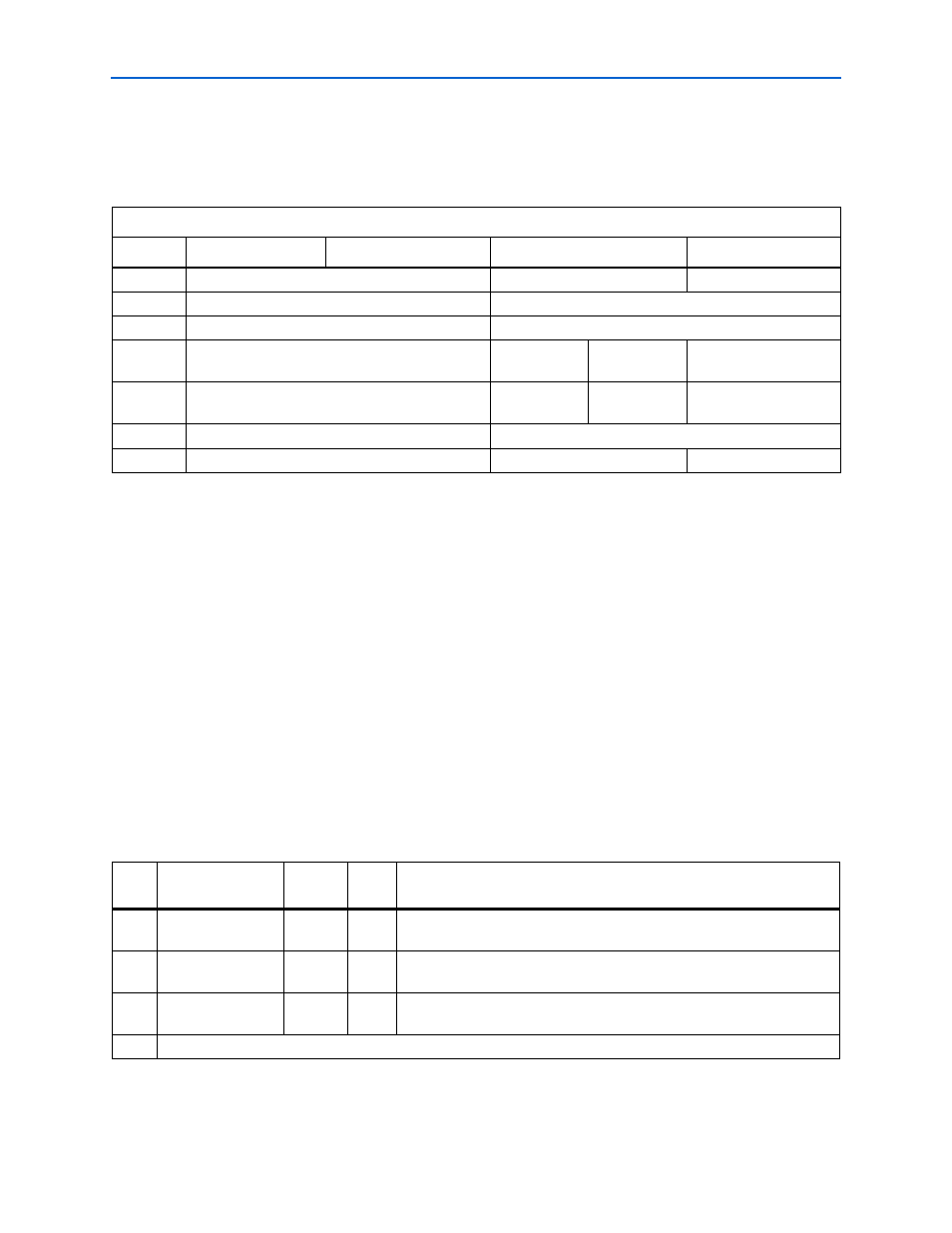

Table 3–13. Primary Interface Capabilities Block Format

HyperTransport Slave/Primary Interface Capabilities Block Format

Address

Byte 3

Byte 2

Byte1

Byte 0

+00

Command

Capabilities Pointer

Capabilities ID

+04

+08

+0C

Link Frequency Cap 0

Link Error 0

Link Freq 0

+10

Link Frequency Cap 1

Link Error 1

Link Freq 1

+14

Enumeration Scratch Pad

+18

Reserved

Mem Limit Upper

Mem Base Upper

Notes to

:

(1) The register is read/write in the HyperTransport MegaCore function.

(2) The register is a read-only register in the HyperTransport MegaCore function.

(3) The configuration register is not used by the HT specification. The register is a read-only register, and Read returns 0s.

(4) The register is not supported in the HyperTransport MegaCore function. The register is a read-only register and Read returns 0s.

Table 3–14. PCI Command Register (Offset 0x04) (Part 1 of 2)

Bits

Name

Register

Type

Reset

Used

Description

0

I/O Space Enable

R/W

Warm

Must be set for the device to claim non-compatibility accesses to I/O

address space

1

Memory Space

Enable

R/W

Warm

Must be set for the device to claim non-compatibility accesses to memory

address space.

2

Bus Master Enable

R/W

Warm

Must be set for the device to issue memory or I/O requests onto the HT

chain.

7:3

Reserved