Altera HyperTransport MegaCore Function User Manual

Page 42

3–16

Chapter 3: Specifications

HyperTransport MegaCore Function Specification

HyperTransport MegaCore Function User Guide

© November 2009

Altera Corporation

Preliminary

1

The following description distinguishes between an HT packet and an Atlantic

packet. An HT packet is defined as indicated in the HT specification with various

types including 32-bit commands, 64-bit commands, or various size data packets. An

Atlantic packet, however, contains one or two HT packets. An Atlantic packet can

contain only a single HT command packet (32- or 64-bit), or a single HT command

packet followed by its associated HT data packet.

HT Link Rx Signals

The HT link Rx signals are differential pair signals.

name for each pair, and the same is true of the HyperTransport MegaCore port

declarations. These signals must be assigned the HyperTransport I/O standard in the

Quartus II software; the software creates the differential pair automatically during

compilation.

HT Link System Signals

describes the HT link system signals. These signals are 2.5-V tolerant

LVCMOS. The HyperTransport MegaCore function does not implement the optional

HT power management signals,

LDTSTOP#

and

LDTREQ#

.

HT Link Tx Signals

The HT link Tx signals are differential pair signals.

name for each pair, and the same is true of the HyperTransport MegaCore port

declarations. These signals must be assigned the HyperTransport I/O standard in the

Quartus II software; the software creates the differential pair automatically during

compilation.

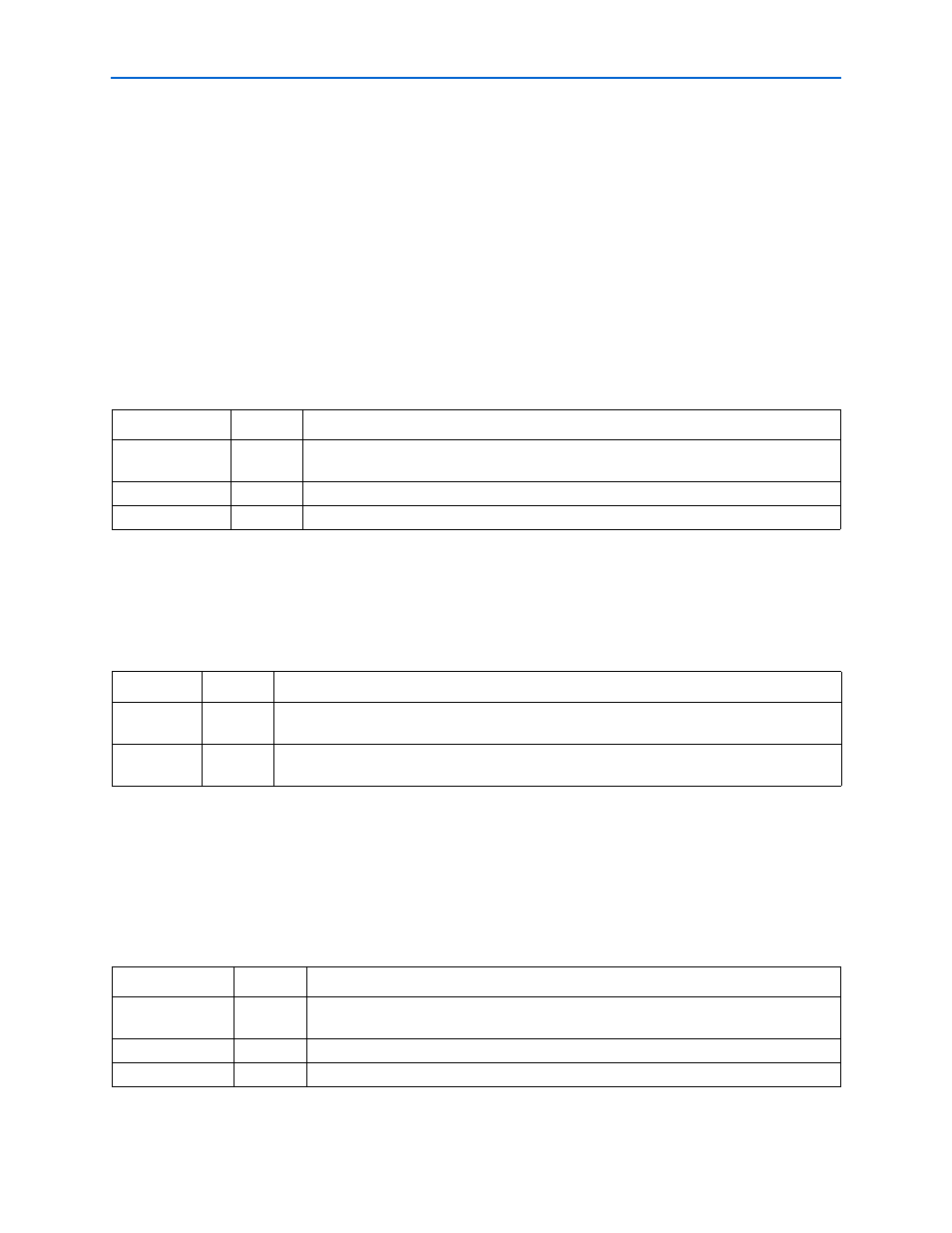

Table 3–2. HT Link Rx Signals

Signal Name

Direction

Description

RxClk_i

Input

RxClk_i

is the received HT clock and is used to clock the

RxCAD_i

and

RxCTL_i

inputs.

RxCAD_i[7:0]

Input

RxCAD_i[7:0]

is the received HT command, address, and data bus.

RxCTL_i

Input

RxCTL_i

is the received HT control signal.

Table 3–3. HT Link System Signals

Signal Name

Direction

Description

Rstn

Input

Rstn

is the HT

Reset#

signal. HT allows it to be a wired

OR

signal with multiple drivers,

however, the HyperTransport MegaCore function treats it as input only.

PwrOk

Input

PwrOk

is the HT power okay signal. HT allows it to be a wired

OR

signal with multiple drivers,

however, the HyperTransport MegaCore treats it as input only.

Table 3–4. HT Link Tx Signals

Signal Name

Direction

Description

TxClk_o

Output

TxClk_o

is the transmitted HT clock and is center-aligned with respect to the

TxCAD_o[7:0]

and

TxCTL_

o signals.

TxCAD_o[7:0]

Output

TxCAD_o[7:0]

is the transmitted HT command, address, and data bus.

TxCTL_o

Output

TxCTL_o

is the transmitted HT control signal.