Altera HyperTransport MegaCore Function User Manual

Page 53

Chapter 3: Specifications

3–27

HyperTransport MegaCore Function Specification

© November 2009

Altera Corporation

HyperTransport MegaCore Function User Guide

Preliminary

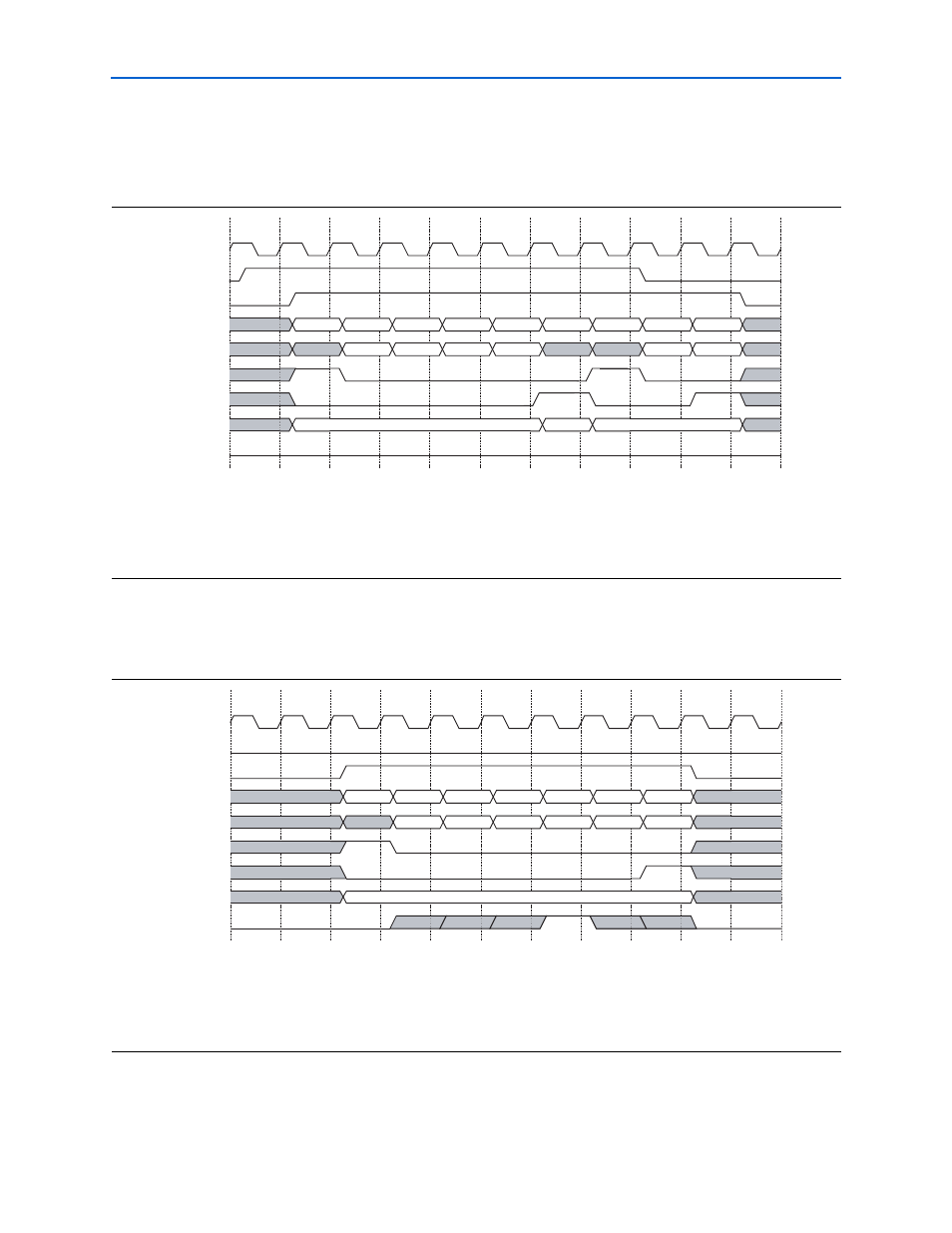

shows two commands transferred back-to-back across the Tx response

buffer interface. A 36-byte read response is transferred followed by a 16-byte read

response.

shows how the Tx Buffer

WrRjct_o

output can be triggered by

attempting to write to a Tx buffer when

Dav_o

is not asserted.

Figure 3–16. Two Streamed Commands on Tx Response Buffer Interface Timing Diagram

Notes to

:

(1)

Dav_o

goes low in this example to indicate the TxResp buffer is full and cannot accept a subsequent command. However, the user application

still asserts

DatEna_i

to complete the current command.

(2)

Dat_i[63:32]

is not valid because the read response command is only 4 bytes.

Mty_i[2:0]

is still 3’b000 because

Eop_i

is not asserted.

(3)

Dat_i[63:32]

is not valid because the data is an odd number of DWORDS in length.

Mty_i[2:0]

is 3’b100 because

Eop_i

is asserted.

2

3

4

5

6

7

9

10

RefClk

Dav_o

8

1

DatEna_i

Dat_i[31:0]

Dat_i[63:32]

Sop_i

Eop_i

WrRjct_o

Mty_i[2:0]

11

RdResp

DW0

DW2

DW4

DW6

DW1

DW3

DW5

DW7

0b000

(1)

(2)

DW8

(3)

0b100

RdResp

DWa

DWc

DWb

DWd

(2)

0b000

Figure 3–17. Tx Buffer Write Reject Timing Diagram

Notes to

:

(1) In this example,

DatEna_i

is asserted without

Dav_o

being asserted, leading to an overrun of the Tx buffer.

(2)

Dat_o[63:32]

is not valid in this example because the command is only a read response.

(3)

WrRjct_o

is asserted because

DatEna_i

was asserted with

Dav_o

. The exact clock cycle in which

WrRjct_o

is asserted varies due to

internal buffer conditions.

2

3

4

5

6

7

9

10

RefClk

Dav_o

8

1

DatEna_i

Dat_i[31:0]

Dat_i[63:32]

Sop_i

Eop_i

WrRjct_o

Mty_i[2:0]

11

(1)

RdResp

DW0

DW2

DW4

DW6

DW1

DW3

DW5

DW7

0b000

(2)

(3)

DW8

DW10

DW9

DW11