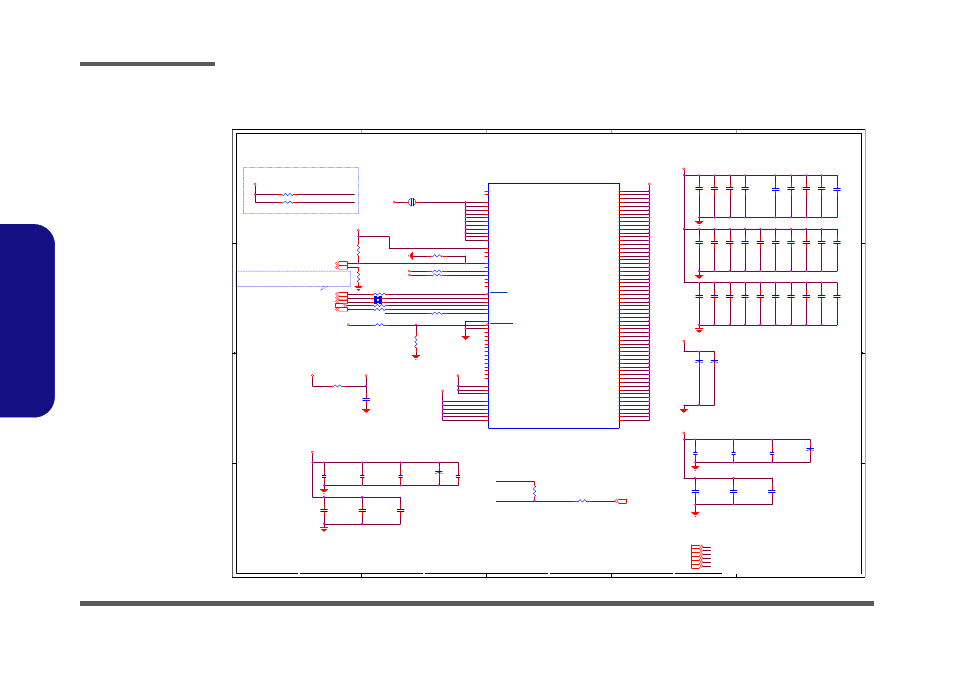

Processor 8/11, Sheet 9 of 42 processor 8/11, B.schematic diagrams – Eurocom Armadillo 2 User Manual

Page 54: ᙔ!ϻ!ႝ!တ!!dmfwp!dp, 32a 1.4a, Processor core power

Schematic Diagrams

B - 10 Processor 8/11

B.Schematic Diagrams

Processor 8/11

5

5

4

4

3

3

2

2

1

1

D

D

C

C

B

B

A

A

PROCESSOR CORE POWER

RESISTOR STUFFING OPTIONS ARE

PROVIDED FOR TESTING PURPOSES

CAD Note: H_CPU_SVIDALRT_R_N

Place the PU resistors close to CPU

SVID Signals

4.2A

4.2A

32A

1.4A

6-71-W8400-D04A

V_VCCDDQ_R

H_CPU_SVIDALRT_R_N

H_CPU_SVIDCLK_R

H_CPU_SVIDDAT_R

H_VR_READY

H_CPU_SVIDALRT#

H_CPU_SVIDDAT

H_VR_ENABLE

H_VR_READY

PW R_DEBUG_N

VCC_SENSE

VCCIN

VCCIN

VCCIN

VCCIN

1.05S_VCCST

1.05S_VCCST

1.05VS

1.05S_VCCST

VCCIN

VCCIOA_OUT

VCCIO_OUT

1.05S_VCCST

V_VCCDDQ

V_VCCDDQ

V_VCCDDQ

VCC_SENSE

36

VSS_SENSE

11,36

H_CPU_SVIDCLK

36

H_CPU_SVIDDAT

36

H_CPU_SVIDALRT#

36

H_VR_ENABLE

36

H_VCCST_PW RGD

2

1.05VS

5,10,32

V_VCCDDQ

2,3,13,14,35,37

VCCIN

36

VCCIOA_OUT

2

VCCIO_OUT

8

VR_READY 36

1.05S_VCCST

2,7,36

Title

Size

Document Number

Rev

Date:

Sheet

of

1.0

[09] HASWELL ULT POWER 1

A3

9

42

Thursday, December 18, 2014

ᙔ!Ϻ!ႝ!တ!!DMFWP!DP/

SCHEMATIC1

Title

Size

Document Number

Rev

Date:

Sheet

of

1.0

[09] HASWELL ULT POWER 1

A3

9

42

Thursday, December 18, 2014

ᙔ!Ϻ!ႝ!တ!!DMFWP!DP/

SCHEMATIC1

Title

Size

Document Number

Rev

Date:

Sheet

of

1.0

[09] HASWELL ULT POWER 1

A3

9

42

Thursday, December 18, 2014

ᙔ!Ϻ!ႝ!တ!!DMFWP!DP/

SCHEMATIC1

+

C582

*330UF_2.5V_6.6*6.6*4.2

C545

22u_6.3V_X5R_08

C468

22u_6.3V_X5R_08

C758

0.01u_50V_X7R_04

C70

22u_6.3V_X5R_08

R102

150_1%_04

C86

22u_6.3V_X5R_08

R412

0_06

C461

22u_6.3V_X5R_08

C152

22u_6.3V_X5R_08

C414

22u_6.3V_X5R_08

R423

0_04

C231

10u_6.3V_X5R_06

HSW_ULT_DDR3L

HSW ULT POWER

12 OF 19

U29L

VCCIO_OUT

A59

VCCIOA_OUT

E20

RSVD

AD23

RSVD

AB23

RSVD

AC58

VCC

F59

VDDQ

AY44

VDDQ

AY40

VDDQ

AY35

RSVD

AA59

RSVD

U59

RSVD

V59

RSVD

AG58

RSVD

AC59

RSVD

AE60

RSVD

AD59

VCCST

AC22

VDDQ

AY50

RSVD

N58

VCC_SENSE

E63

RSVD

AA23

RSVD

AE59

VCCST_PWRGD

B59

VR_READY

C59

VR_EN

F60

VDDQ

AR48

VDDQ

AP43

VDDQ

AN33

VDDQ

AJ37

VDDQ

AJ33

VDDQ

AJ31

VDDQ

AH26

RSVD

J58

RSVD

L59

VCC

C24

VCC

C28

VCC

C32

VCC

AG57

VCC

W57

VCC

U57

VCC

M23

VCC

M57

VCC

P57

VCC

L22

VCC

K57

VCC

H23

VCC

J23

VCC

G55

VCC

G57

VCC

G49

VCC

G51

VCC

G53

VCC

G45

VCC

G47

VCC

G43

VCC

G39

VCC

G41

VCC

G37

VCC

G35

VCC

G33

VCC

G29

VCC

G31

VCC

G27

VCC

G25

VCC

G23

VCC

F52

VCC

F56

VCC

F48

VCC

F44

VCC

F40

VCC

F28

VCC

F32

VCC

F36

VCC

F24

VCC

E57

VCC

E51

VCC

E53

VCC

E55

VCC

E47

VCC

E49

VCC

E41

VCC

E43

VCC

E45

VCC

E37

VCC

E39

VCC

E31

VCC

E33

VCC

E35

VCC

E27

VCC

E29

VCC

C56

VCC

E23

VCC

E25

VCC

C48

VCC

C52

VCC

C36

VCC

C40

VCC

C44

VCC

K23

VCC

AD57

VCC

AB57

VCCST

AE23

VCCST

AE22

VIDSOUT

L63

VIDSCLK

N63

VIDALERT

L62

VSS

P62

RSVD_TP

P60

RSVD_TP

P61

RSVD_TP

N59

RSVD_TP

N61

RSVD

T59

RSVD

AD60

VSS

D63

PWR_DEBUG

H59

C530

*22u_6.3V_X5R_08

R416

0_04

C75

22u_6.3V_X5R_08

R437

*0_04

C149

22u_6.3V_X5R_08

PJ11

*OPEN-5mm

1

2

C76

22u_6.3V_X5R_08

+

C424

330UF_2.5V_6.6*6.6*4.2

C77

22u_6.3V_X5R_08

C529

22u_6.3V_X5R_08

C140

22u_6.3V_X5R_08

C460

22u_6.3V_X5R_08

R470

*10mil_short

C433

22u_6.3V_X5R_08

C215

*10u_6.3V_X5R_06

R474

75_04

C214

10u_6.3V_X5R_06

C434

22u_6.3V_X5R_08

C534

*22u_6.3V_X5R_08

R424

0_04

C417

22u_6.3V_X5R_08

R473

43.2_1%_04

R103

*10K_04

R442

100_04

C87

22u_6.3V_X5R_08

C546

22u_6.3V_X5R_08

+

C447

*330UF_2.5V_6.6*6.6*4.2

C111

22u_6.3V_X5R_08

C112

22u_6.3V_X5R_08

R158

0_04

C223

*10u_6.3V_X5R_06

C450

22u_6.3V_X5R_08

C110

22u_6.3V_X5R_08

R81

0_04

C71

22u_6.3V_X5R_08

C232

10u_6.3V_X5R_06

C148

22u_6.3V_X5R_08

+

C580

330UF_2.5V_6.6*6.6*4.2

R68

10K_04

C150

22u_6.3V_X5R_08

C139

22u_6.3V_X5R_08

C413

22u_6.3V_X5R_08

C459

22u_6.3V_X5R_08

R94

0_04

C72

22u_6.3V_X5R_08

R482

*10mil_short

C151

22u_6.3V_X5R_08

C224

10u_6.3V_X5R_06

C88

22u_6.3V_X5R_08

C535

22u_6.3V_X5R_08

R471

110_1%_04

C469

22u_6.3V_X5R_08

R91

100_04

Sheet 9 of 42

Processor 8/11