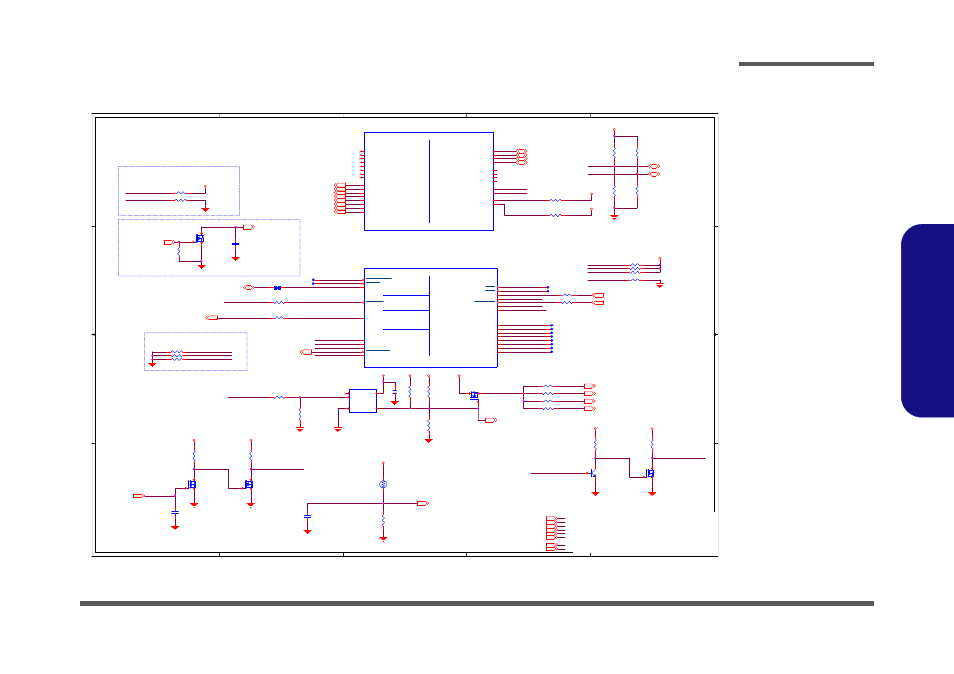

Processor 1/11, Sheet 2 of 42 processor 1/ 11, B.schematic diagrams – Eurocom Armadillo 2 User Manual

Page 47: Schematic diagrams processor 1/11 b - 3, ᙔ!ϻ!ႝ!တ!!dmfwp!dp

Schematic Diagrams

Processor 1/11 B - 3

B.Schematic Diagrams

Processor 1/11

Sheet 2 of 42

Processor 1/ 11

5

5

4

4

3

3

2

2

1

1

D

D

C

C

B

B

A

A

PU/PD for JTAG signals

CAD Note: Capacitor need to be placed

close to buffer output pin

Processor Pullups/Pull downs

TRACE WIDTH 10MIL, LENGTH <500MILS

DDR3 Compensation Signals

L <=100MILS,

W=20MILS,

SPACE=25MILS

SINGLE=50ohm, DIFF=85ohm, L <=10"

8/30

1:2 (4mils:8mils)

CLOSE TO CHIP 500mil

6-71-W8400-D04A

10K_1%

EDP_AUXN

EDP_AUXN

EDP_AUXP

XDP_TDI_R

XDP_BPM6

XDP_BPM1

XDP_BPM2

XDP_BPM4

XDP_BPM3

XDP_BPM5

XDP_BPM7

XDP_BPM0

XDP_TCLK

XDP_TDI_R

XDP_TDO_R

XDP_TMS

XDP_TRST#

XDP_PRDY#

XDP_PREQ#

XDP_TMS

XDP_TCLK

PROC DETECT#

H_CATERR#

H_PECI_ISO

H_PROCHOT#

H_PROCHOT#_D

H_PROCHOT#

H_CPUPW RGD_R

H_PROCHOT#

H_CPUPW RGD_R

SM_RCOMP_1

CPUDRAMRST#

SM_RCOMP_2

SM_RCOMP_0

SM_RCOMP_1

SM_RCOMP_0

SM_RCOMP_2

DDR_PG_CTRL

XDP_TDO_R

EDP_AUXP

DDR_VTT_PG_CTRL

DDR_PG_CTRL_R

M_A_B_DIMM_ODT

DDR_PG_CTRL

H_VCCST_PW RGD

H_VCCST_PW RGD

EDP_UTIL

EDP_RCOMP

DDR_PG_CTRL

DDR_VTT_PG_CTRL

3.3VS

VCCIOA_OUT

3.3VS

1.05VS_VCCST

1.05S_VCCST

V_VCCDDQ

VDD5

V_VCCDDQ

1.05S_VCCST

3.3V

3.3V

3.3VA

3.3VA

3.3VA

EDP_TXN_0 22

EDP_TXP_1 22

EDP_TXN_1 22

EDP_TXP_0 22

EDP_AUXN 22

EDP_AUXP 22

3.3VS

4,5,6,7,8,10,13,14,15,16,22,23,24,25,26,28,29,30,32,34,36

VCCIOA_OUT

9

HDMI2_CLKCN

25

HDMI2_CLKCP

25

HDMI2_C1CN

25

HDMI2_C1CP

25

HDMI2_C0CN

25

HDMI2_C0CP

25

HDMI2_C2CN

25

HDMI2_C2CP

25

PCH_JTAG_TCK 4

CPUDRAMRST#

13

H_PECI

28

H_PROCHOT_EC

28

XDP_TRST_CPU_N 4

H_PROCHOT# 36

M_B_DIM0_ODT1 14

M_A_DIM0_ODT0 13

M_A_DIM0_ODT1 13

DDR_VTT_PG_CTRL 35

M_B_DIM0_ODT0 14

1.05S_VCCST

7,9,36

VCCIO_OUT

8,9

3.3V

15,20,23,24,26,27,29,30,32,34,35,37

V_VCCDDQ

3,9,13,14,35,37

H_VCCST_PW RGD

9

1.05VS_PW RGD

6,32,34

THERM_VOLT 28

VDD5

27,32,33,34

3.3VA

4,5,6,7,8,10,27,30

Title

Size

Document Number

Rev

Date:

Sheet

of

1.0

[02] HASWELL ULT (DISPLAY,MISC,JTAG,CLK)

A3

2

42

Friday, July 11, 2014

ᙔ!Ϻ!ႝ!တ!!DMFWP!DP/

SCHEMATIC1

Name

Title

Size

Document Number

Rev

Date:

Sheet

of

1.0

[02] HASWELL ULT (DISPLAY,MISC,JTAG,CLK)

A3

2

42

Friday, July 11, 2014

ᙔ!Ϻ!ႝ!တ!!DMFWP!DP/

SCHEMATIC1

Name

Title

Size

Document Number

Rev

Date:

Sheet

of

1.0

[02] HASWELL ULT (DISPLAY,MISC,JTAG,CLK)

A3

2

42

Friday, July 11, 2014

ᙔ!Ϻ!ႝ!တ!!DMFWP!DP/

SCHEMATIC1

Name

C138

470p_50V_X7R_04

R506

51_04

Q6

MTN7002ZHS3

G

D

S

R422

*10K_04

R351

66.5_1%_04

R69

*100K_04

R528

0_04

R523

*100K_04

R154

100K_04

R447

*51_04

C304

0.1u_10V_X5R_04

R319

*220K_1%_04

R352

66.5_1%_04

Q26

*MTN7002ZHS3

G

D

S

R192

100_1%_04

R309

66.5_1%_04

R63

*100K_04

R199

200_1%_04

R117

100K_04

R310

66.5_1%_04

R209

75_1%_04

DDR3L

HSW_ULT_DDR3L

MISC

THERMAL

PWR

JTAG

2 OF 19

U29B

BPM#4

K59

BPM#5

H63

BPM#6

K60

SM_RCOMP0

AU60

BPM#7

J61

BPM#3

H62

BPM#1

H60

BPM#2

H61

BPM#0

J60

PROC_TDO

F62

PROC_TDI

F63

PROC_TMS

E61

PECI

N62

CATERR

K61

PROCPWRGD

C61

PROCHOT

K63

PROC_TRST

E59

PROC_TCK

E60

PRDY

J62

PREQ

K62

SM_PG_CNTL1

AV61

SM_DRAMRST

AV15

SM_RCOMP2

AU61

SM_RCOMP1

AV60

PROC_DETECT

D61

C83

47p_50V_NPO_04

Q11

BSS138

G

D

S

Q4

MTN7002ZHS3

G

D

S

R70

*100K_04

R322

0_04

Q5

MTN7002ZHS3

G

D

S

U22

74AUP1G07GW

NC

1

A

2

GND

3

VCC

5

Y

4

R134

100K_04

R417

*0_04

HSW_ULT_DDR3L

EDP

DDI

1 OF 19

U29A

DDI1_TXN0

C54

DDI1_TXP0

C55

DDI1_TXN1

B58

DDI1_TXP1

C58

DDI1_TXN2

B55

DDI1_TXP2

A55

DDI1_TXN3

A57

EDP_TXP0

B46

EDP_TXN0

C45

EDP_TXN1

A47

EDP_TXP1

B47

EDP_TXN2

C47

EDP_TXP2

C46

EDP_TXN3

A49

EDP_TXP3

B49

EDP_AUXP

B45

EDP_AUXN

A45

DDI1_TXP3

B57

DDI2_TXP1

B54

DDI2_TXP0

C50

DDI2_TXN0

C51

DDI2_TXN1

C53

DDI2_TXN2

C49

DDI2_TXP2

B50

DDI2_TXN3

A53

DDI2_TXP3

B53

EDP_RCOMP

D20

EDP_DISP_UTIL

A43

R95

24.9_1%_04

R418

10K_04

R317

*2M_1%_04

R466

62_04

R483

*10mil_short

R433

*51_04

C523

*0.1u_10V_X7R_04

R323

*0_04

R465

56_1%_04

R318

220K_1%_04

R448

*51_04

R529

*100K_04

PTH1

TH05-3H103FR

1

2

Q27

*2N3904

B

E

C

R62

*100K_04

R513

*0_04

R563

10K_1%_04