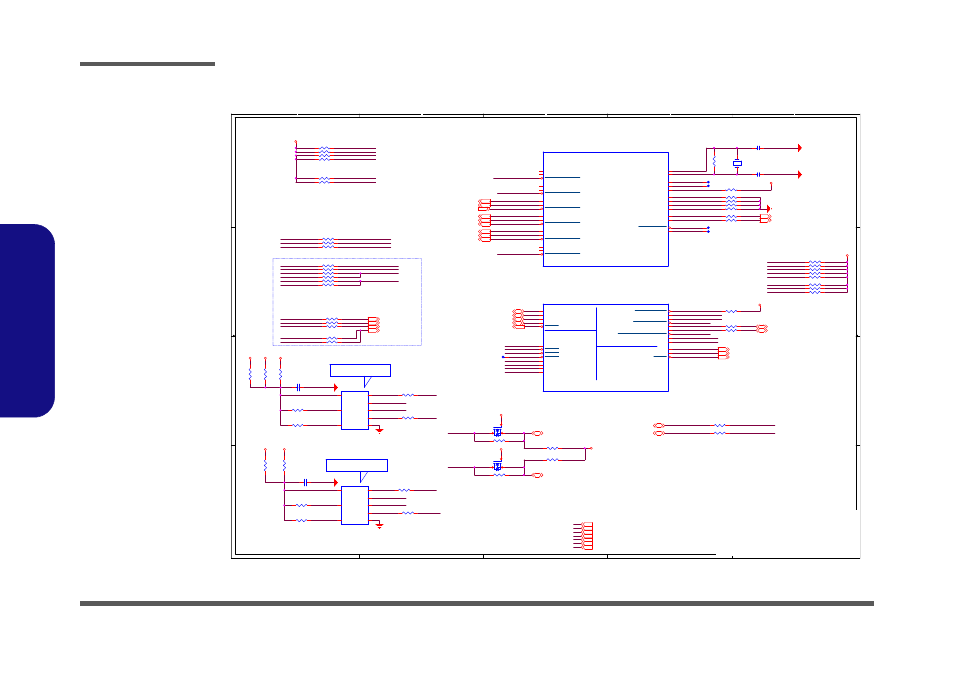

Processor 4/11, Sheet 5 of 42 processor 4/11, B.schematic diagrams – Eurocom Armadillo 2 User Manual

Page 50: Schematic diagrams b - 6 processor 4/11, Bios rom, Bios+me rom, ᙔ!ϻ!ႝ!တ!!dmfwp!dp

5

5

4

4

3

3

2

2

1

1

D

D

C

C

B

B

A

A

Co_Lay

ᓮ

ᓮ

ᓮ

ᓮإ

إ

إ

إહ

હ

હ

હᦤ

ᦤ

ᦤ

ᦤ

Share ROM

100MHz

BIOS ROM

32Mbit

SPI_* = 1.5"~6.5"

SPI_* = 1.5"~6.5"

BIOS+ME ROM

64Mbit

6-71-W8400-D04A

SPI_CS1#

SPI_CS0#

SPI_SO

SPI_CS_0#

SPI_CS1#

SPI_SCLK_R

SPI_SCLK

SPI_W P#_1

SPI_HOLD#_1

PCH_SPI_DQ3

PCH_SPI_DQ2

SPI_SI_R

SPI_SO_R

SPI_HOLD#_0

SPI_W P#_0

SPI_CS_0#

SPI_CS_1#

SPI_SI_R

SPI_SO_R

SPI_SCLK_R

SPI_CS_0#

SPI_CS_1#

SPI_SI_R

SPI_SO_R

PCH_SPI_DQ2

PCH_SPI_DQ3

CL_RST#1

PCH_GPIO73

SMB_CLK

SMB_DATA

DRAMRST_CNTRL

SML1DATA

SML1CLK

SML0_DATA

SML0_CLK

PCH_GPIO11

SML0_CLK

SML0_DATA

SMB_CLK

SMB_DATA

SML1DATA

SML1CLK

PCH_GPIO73

SMB_DATA

SMB_CLK

SPI_SCLK_R

SPI_SI

PCIECLKRQ3#

W LAN_CLKREQ#

PCIECLKRQ2#

PCIECLKRQ4#

XTAL24_OUT

XTAL24_IN

XCLK_BIASRE

TESTLOW 2

TESTLOW 1

TESTLOW 4

TESTLOW 3

LPC_0

LPC_1

CK_XDP_P

CK_XDP_N

RSVD2

RSVD1

LAN_CLKREQ#

PEG_CLKREQ#

SPI_SCLK_B

SPI_SCLK

SPI_SI_B

SPI_SI

SPI_CS1#

SPI_SO

SPI_W P#_1

SPI_HOLD#_1

SPI_SI_M

SPI_SI

SPI_W P#_0

SPI_HOLD#_0

SPI_CS0#

SPI_SO

SPI_SCLK_M

SPI_SCLK

DRAMRST_CNTRL

SMC_CPU_THERM

SML1CLK

SML1DATA

SMD_CPU_THERM

PCIECLKRQ3#

LAN_CLKREQ#

PCIECLKRQ2#

W LAN_CLKREQ#

PCIECLKRQ4#

PEG_CLKREQ#

CL_DATA1

CL_CLK1

3.3VA

3.3VA

3.3VS

3.3VS

3.3VS

3.3VS

1.05VS

3.3V_SPI

3.3V_M

3.3V_M

3.3VA

3.3VA

LPC_AD0

28,29

LPC_AD1

28,29

LPC_AD2

28,29

LPC_AD3

28,29

LPC_FRAME#

28,29

HSPI_SCLK 28

HSPI_CE# 28

HSPI_MSO 28

HSPI_MSI 28

CL_RST#1 24

3.3VS 2,4,6,7,8,10,13,14,15,16,22,23,24,25,26,28,29,30,32,34,36

VDD3 4,6,10,20,24,27,28,29,30,31,32,33,34

SMB_DAT_DDR 13,14,27

SMB_CLK_DDR 13,14,27

PCLK_KBC 28

PCLK_TPM 29

SMC_VGA_THERM 20,28

SMD_VGA_THERM 20,28

1.05VS 9,10,32

3.3V_SPI 10,30

3.3VA 2,4,6,7,8,10,27,30

3.3V_M 6,10,30

RTCVCC 4,6,10

SMC_CPU_THERM

28

SMD_CPU_THERM

28

CLK_PCIE_GLAN

23

CLK_PCIE_GLAN#

23

LAN_CLKREQ#

23

CLK_PCIE_MINI

24

CLK_PCIE_MINI#

24

W LAN_CLKREQ#

24

PEG_CLKREQ#

16

VGA_PEXCLK

16

VGA_PEXCLK#

16

CL_DATA1 24

CL_CLK1 24

Title

Size

Document Number

Rev

Date:

Sheet

of

1.0

[05] HASWELL ULT LPC/SPI/SMB/CL

A3

5

42

Thursday, December 18, 2014

ᙔ!Ϻ!ႝ!တ!!DMFWP!DP/

SCHEMATIC1

Title

Size

Document Number

Rev

Date:

Sheet

of

1.0

[05] HASWELL ULT LPC/SPI/SMB/CL

A3

5

42

Thursday, December 18, 2014

ᙔ!Ϻ!ႝ!တ!!DMFWP!DP/

SCHEMATIC1

Title

Size

Document Number

Rev

Date:

Sheet

of

1.0

[05] HASWELL ULT LPC/SPI/SMB/CL

A3

5

42

Thursday, December 18, 2014

ᙔ!Ϻ!ႝ!တ!!DMFWP!DP/

SCHEMATIC1

C475

18p_50V_NPO_04

R515

*0_04

C187

*0.1u_16V_Y5V_04

T83

R476

0_04

C476

18p_50V_NPO_04

R221

22_04

R207

*3.3K_1%_04

R468

0_04

R205

*0_04

R201

0_04

R204

33_04

R520

*0_04

HSW_ULT_DDR3L

LPC

SMBUS

C-LINK

SPI

7 OF 19

U29G

CL_RST

AF4

CL_DATA

AD2

CL_CLK

AF2

SML1CLK/GPIO75

AU3

SML1DATA/GPIO74

AH3

SML1ALERT/PCHHOT/GPIO73

AU4

SML0DATA

AK1

SML0CLK

AN1

SMBDATA

AH1

SML0ALERT/GPIO60

AL2

SMBCLK

AP2

SMBALERT/GPIO11

AN2

SPI_IO3

AF1

SPI_IO2

Y6

SPI_MISO

AA4

SPI_MOSI

AA2

SPI_CS2

AC2

SPI_CS1

Y4

SPI_CLK

AA3

SPI_CS0

Y7

LFRAME

AV12

LAD3

AW11

LAD2

AY12

LAD1

AW12

LAD0

AU14

R516

499_1%_04

R247

*0_04

R462

0_04

R182

10K_04

R96

10K_04

R197

*33_04

R469

33_04

R478

0_04

R524

10K_04

R498

2.2K_04

R519

10K_04

R499

2.2K_04

C186

0.1u_16V_Y5V_04

R125

*0_04

R497

*0_04

R202

3.3K_1%_04

X3

RG24MHZ

1

2

R71

3.01K_1%_04

R120

*10K_04

R508

10K_04

U35

*A25LQ32A

PCB Footprint = M-SOP8B

CE#

1

SO

2

WP#

3

VSS

4

SI

5

SCK

6

HOLD#

7

VDD

8

R485

33_04

R181

10K_04

R73

10K_04

U34

EON 64M(EN25QH64)

PCB Footprint = M-SOP8B

CE#

1

SO

2

WP#

3

VSS

4

SI

5

SCK

6

HOLD#

7

VDD

8

R200

*0_04

R172

*3.3K_1%_04

R490

33_04

R98

10K_04

R530

*0_04

R206

*0_04

R504

499_1%_04

R220

22_04

R525

2.2K_04

R250

*0_04

R121

0_04

R203

33_04

R111

33_04

R511

*1K_04

R153

3.3K_1%_04

R492

10K_04

R455

10K_04

R491

*33_04

S

D

G

Q25B

MTDN7002ZHS6R

5

3

4

R195

*0_04

R198

*33_04

R521

2.2K_04

CLOCK

SIGNALS

HSW_ULT_DDR3L

6 OF 19

U29F

CLKOUT_PCIE_N1

B41

CLKOUT_PCIE_P1

A41

PCIECLKRQ1/GPIO19

Y5

PCIECLKRQ0/GPIO18

U2

CLKOUT_PCIE_P0

C42

CLKOUT_ITPXDP

B35

CLKOUT_LPC_0

AN15

CLKOUT_LPC_1

AP15

PCIECLKRQ4/GPIO22

U5

CLKOUT_PCIE_P4

B39

CLKOUT_PCIE_N4

A39

PCIECLKRQ3/GPIO21

N1

CLKOUT_PCIE_N0

C43

XTAL24_OUT

B25

XTAL24_IN

A25

PCIECLKRQ5/GPIO23

T2

CLKOUT_PCIE_P5

A37

CLKOUT_PCIE_N5

B37

CLKOUT_PCIE_P3

C37

CLKOUT_PCIE_N3

B38

PCIECLKRQ2/GPIO20

AD1

CLKOUT_PCIE_N2

C41

CLKOUT_PCIE_P2

B42

DIFFCLK_BIASREF

C26

RSVD

K21

RSVD

M21

TESTLOW_C35

C35

TESTLOW_C34

C34

TESTLOW_AK8

AK8

TESTLOW_AL8

AL8

CLKOUT_ITPXDP_P

A35

S

D

G

Q25A

MTDN7002ZHS6R

2

6

1

R477

33_04

R124

0_04

R89

10K_04

R83

10K_04

R426

1M_04

R105

*33_04

R189

10K_04

Sheet 5 of 42

Processor 4/11

Schematic Diagrams

B - 6 Processor 4/11

B.Schematic Diagrams

Processor 4/11