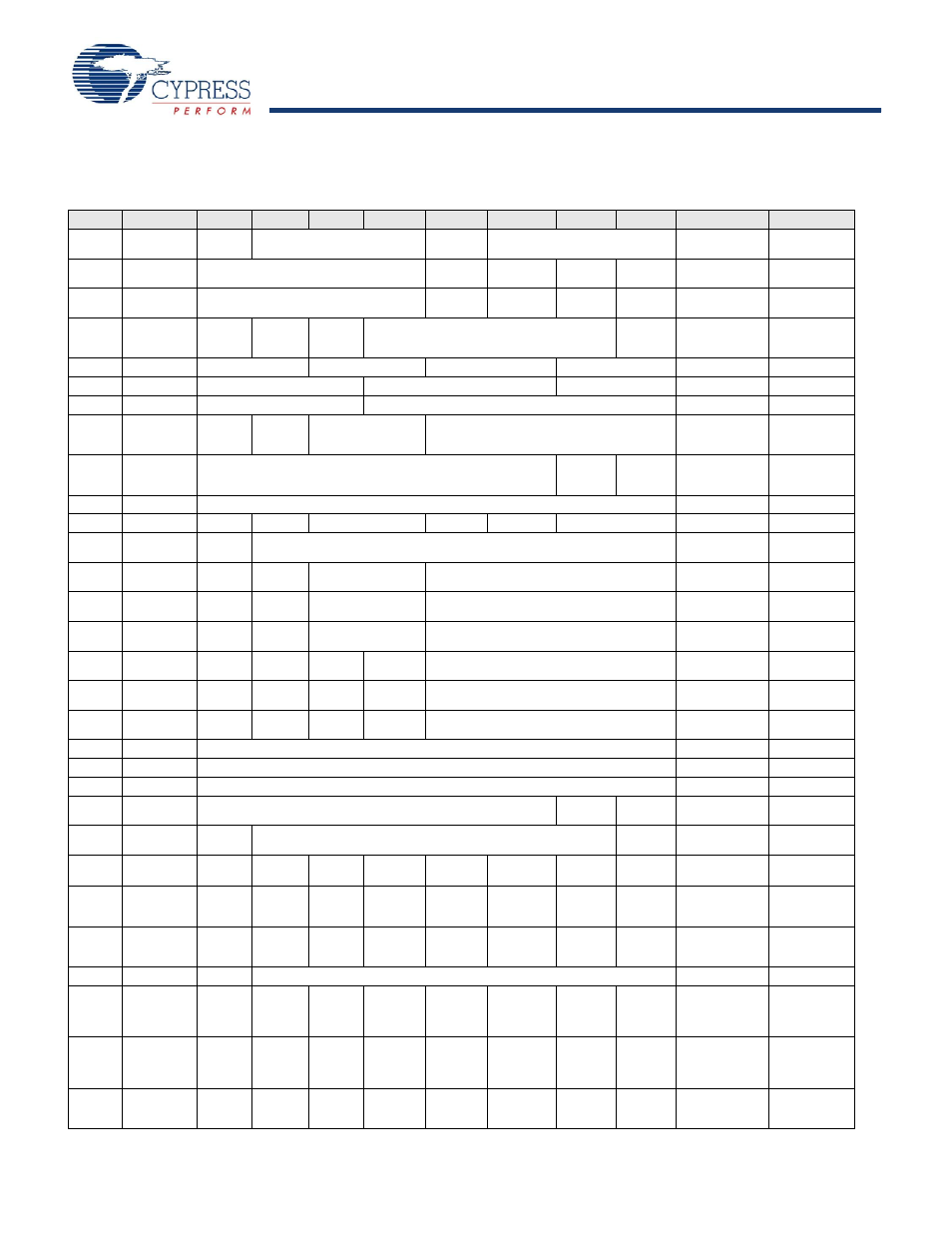

Register summary – Cypress enCoRe CY7C63310 User Manual

Page 65

CY7C63310, CY7C638xx

Document 38-08035 Rev. *K

Page 65 of 83

2A

TMRCR

First Edge

Hold

8-bit capture Prescale

Cap0 16bit

Enable

Reserved

bbbbb---

00000000

2B

TCAPINTE

Reserved

Cap1 Fall

Active

Cap1 Rise

Active

Cap0 Fall

Active

Cap0 Rise

Active

----bbbb

00000000

2C

TCAPINTS

Reserved

Cap1 Fall

Active

Cap1 Rise

Active

Cap0 Fall

Active

Cap0 Rise

Active

----bbbb

00000000

30

CPUCLKCR Reserved

USB

CLK/2

Disable

USB CLK

Select

Reserved

CPU

CLK Select

-bb----b

00010000

31

ITMRCLKCR

TCAPCLK Divider

TCAPCLK Select

ITMRCLK Divider

ITMRCLK Select

bbbbbbbb

10001111

32

CLKIOCR

Reserved

Reserved

CLKOUT Select

---bbbbb

00000000

34

IOSCTR

foffset[2:0]

Gain[4:0]

bbbbbbbb

000ddddd

36

LPOSCTR

32 kHz

Low

Power

Reserved 32 kHz Bias Trim [1:0]

32 kHz Freq Trim [3:0]

b-bbbbbb

dddddddd

39

OSCLCKCR

Reserved

Fine Tune

Only

USB

Osclock

Disable

------bb

00000000

3C

SPIDATA

SPIData[7:0]

bbbbbbbb

00000000

3D

SPICR

Swap

LSB First

Comm Mode

CPOL

CPHA

SCLK Select

bbbbbbbb

00000000

40

USBCR

USB

Enable

Device Address[6:0]

bbbbbbbb

00000000

41

EP0CNT

Data

Toggle

Data Valid

Reserved

Byte Count[3:0]

bbbbbbbb

00000000

42

EP1CNT

Data

Toggle

Data Valid

Reserved

Byte Count[3:0]

bbbbbbbb

00000000

43

EP2CNT

Data

Toggle

Data Valid

Reserved

Byte Count[3:0]

bbbbbbbb

00000000

44

EP0MODE

Setup

rcv’d

IN rcv’d

OUT rcv’d ACK’d trans

Mode[3:0]

ccccbbbb

00000000

45

EP1MODE

Stall

Reserved

NAK Int

Enable

Ack’d trans

Mode[3:0]

b-bcbbbb

00000000

46

EP2MODE

Stall

Reserved

NAK Int

Enable

Ack’d trans

Mode[3:0]

b-bcbbbb

00000000

50–57

EP0DATA

Endpoint 0 Data Buffer [7:0]

bbbbbbbb

????????

58–5F

EP1DATA

Endpoint 1 Data Buffer [7:0]

bbbbbbbb

????????

60–67

EP2DATA

Endpoint 2 Data Buffer [7:0]

bbbbbbbb

????????

73

VREGCR

Reserved

Keep Alive

VREG

Enable

------bb

00000000

74

USBXCR

USB Pull

up Enable

Reserved

USB Force

State

b------b

00000000

DA

INT_CLR0

GPIO Port

1

Sleep

Timer

INT1

GPIO Port

0

SPI

Receive

SPI Transmit

INT0

POR/LVD

bbbbbbbb

00000000

DB

INT_CLR1

TCAP0

Prog

Interval

Timer

1-ms

Timer

USB Active USB Reset

USB EP2

USB EP1

USB EP0

bbbbbbbb

00000000

DC

INT_CLR2

Reserved Reserved GPIO Port

3

GPIO Port 2 PS/2 Data

Low

INT2

16-bit

Counter

Wrap

TCAP1

-bbbbbbb

00000000

DE

INT_MSK3

ENSWINT

Reserved

b-------

00000000

DF

INT_MSK2

Reserved Reserved GPIO Port

3

Int Enable

GPIO Port 2

Int Enable

PS/2 Data

Low Int

Enable

INT2

Int Enable

16-bit

Counter

Wrap

Int Enable

TCAP1

Int Enable

-bbbbbbb

00000000

E1

INT_MSK1

TCAP0

Int Enable

Prog

Interval

Timer

Int Enable

1-ms

Timer

Int Enable

USB Active

Int Enable

USB Reset

Int Enable

USB EP2

Int Enable

USB EP1

Int Enable

USB EP0

Int Enable

bbbbbbbb

00000000

E0

INT_MSK0

GPIO Port

1

Int Enable

Sleep

Timer

Int Enable

INT1

Int Enable

GPIO Port 0

Int Enable

SPI

Receive

Int Enable

SPI Transmit

Int Enable

INT0

Int Enable

POR/LVD

Int Enable

bbbbbbbb

00000000

24. Register Summary

(continued)

The XIO bit in the CPU Flags Register must be set to access the extended register space for all registers above 0xFF.

Addr

Name

7

6

5

4

3

2

1

0

R/W

Default