Cypress enCoRe CY7C63310 User Manual

Page 38

CY7C63310, CY7C638xx

Document 38-08035 Rev. *K

Page 38 of 83

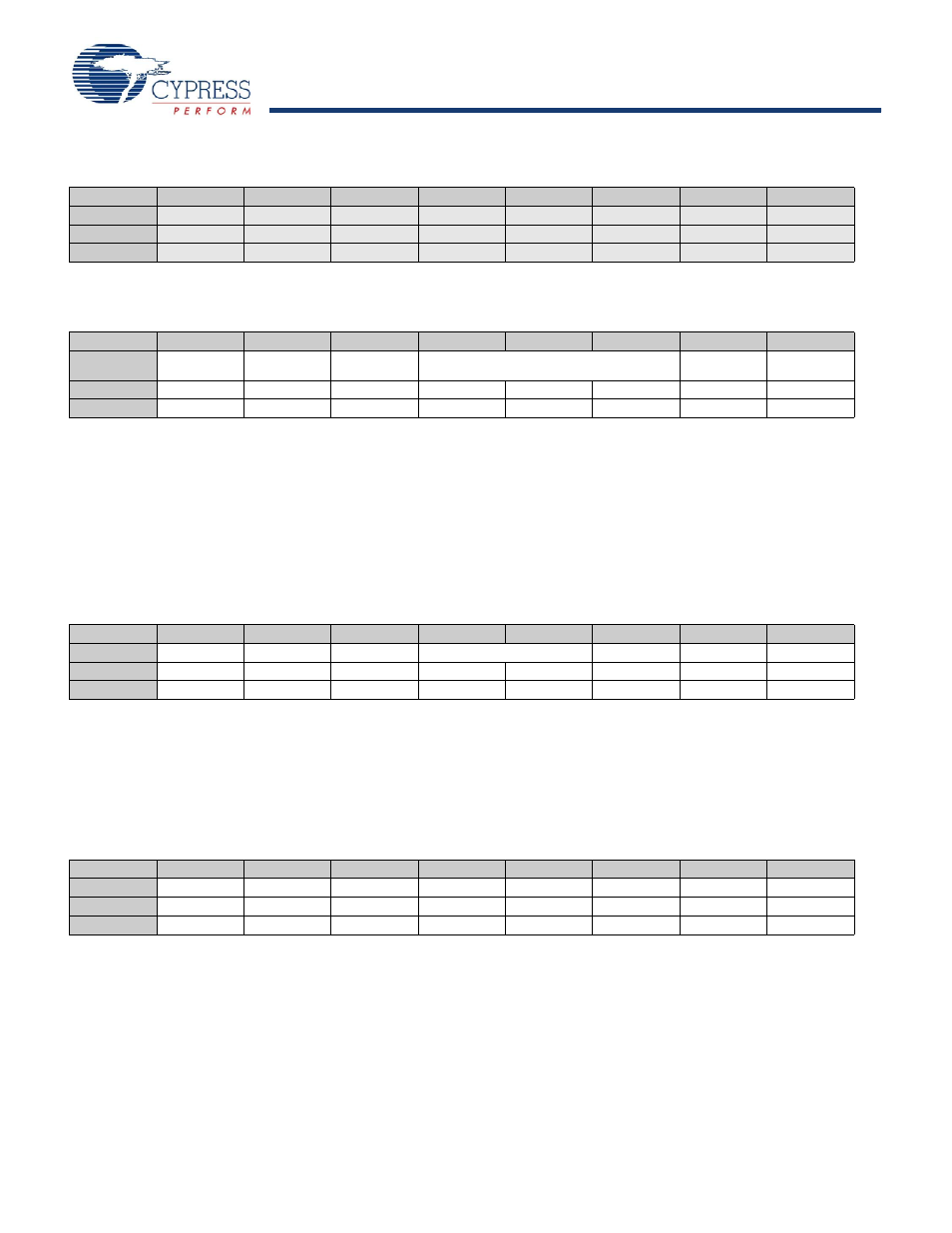

Table 14-9. P0.7 Configuration (P07CR) [0x0C] [R/W]

Bit #

7

6

5

4

3

2

1

0

Field

Reserved

Int Enable

Int Act Low

TTL Thresh

Reserved

Open Drain

Pull up Enable

Output Enable

Read/Write

–

R/W

R/W

R/W

–

R/W

R/W

R/W

Default

0

0

0

0

0

0

0

0

This register controls the operation of pin P0.7. The P0.7 pin only exists in the CY7C638(1/2/3)3.

Table 14-10. P1.0/D+ Configuration (P10CR) [0x0D] [R/W]

Bit #

7

6

5

4

3

2

1

0

Field

Reserved

Int Enable

Int Act Low

Reserved

PS/2 Pull up

Enable

Output Enable

Read/Write

R/W

R/W

R/W

–

–

–

R/W

R/W

Default

0

0

0

0

0

0

0

0

This register controls the operation of the P1.0 (D+) pin when the USB interface is not enabled, allowing the pin to be used as

a PS2 interface or a GPIO. See

on page 58 for information on enabling the USB. When the USB is enabled, none of

the controls in this register have any affect on the P1.0 pin.

Note

The P1.0 is an open drain only output. It can actively drive a signal low, but cannot actively drive a signal high.

Bit 1:

PS/2 Pull up Enable

0 = Disable the 5K ohm pull up resistors

1 = Enable 5K ohm pull up resistors for both P1.0 and P1.1. Enable the use of the P1.0 (D+) and P1.1 (D–) pins as a PS2 style

interface.

Table 14-11. P1.1/D– Configuration (P11CR) [0x0E] [R/W]

Bit #

7

6

5

4

3

2

1

0

Field

Reserved

Int Enable

Int Act Low

Reserved

Open Drain

Reserved

Output Enable

Read/Write

–

R/W

R/W

–

–

R/W

–

R/W

Default

0

0

0

0

0

0

0

0

This register controls the operation of the P1.1 (D–) pin when the USB interface is not enabled, allowing the pin to be used as

a PS2 interface or a GPIO. See

on page 58 for information on enabling USB. When USB is enabled, none of the

controls in this register have any affect on the P1.1 pin. When USB is disabled, the 5K ohm pull up resistor on this pin may be

enabled by the PS/2 Pull Up Enable bit of the P10CR Register (

)

Note

There is no 2 mA sourcing capability on this pin. The pin can only sink 5 mA at V

OL3

(See section

Table 14-12. P1.2 Configuration (P12CR) [0x0F] [R/W]

Bit #

7

6

5

4

3

2

1

0

Field

CLK Output

Int Enable

Int Act Low

TTL Threshold

Reserved

Open Drain

Pull up Enable

Output Enable

Read/Write

R/W

R/W

R/W

R/W

–

R/W

R/W

R/W

Default

0

0

0

0

0

0

0

0

This register controls the operation of the P1.2.

Bit 7:

CLK Output

0 = The internally selected clock is not sent out onto P1.2 pin

1 = When CLK Output is set, the internally selected clock is sent out onto P1.2 pin

Note:

Table 10-7, “Clock IO Config (CLKIOCR) [0x32] [R/W],”

on page 26 is used to select the external or internal clock in enCoRe

II devices