3 writeblock function, 4 eraseblock function, 5 protectblock function – Cypress enCoRe CY7C63310 User Manual

Page 16

CY7C63310, CY7C638xx

Document 38-08035 Rev. *K

Page 16 of 83

9.5.3 WriteBlock Function

The WriteBlock function is used to store data in the Flash. Data

is moved 64 bytes at a time from SRAM to Flash using this

function. The WriteBlock function first checks the protection bits

and determines if the desired BLOCKID is writable. If write

protection is turned on, the WriteBlock function exits setting the

accumulator and KEY2 back to 00h. KEY1 has a value of 01h,

indicating a write failure. The configuration of the WriteBlock

function is straightforward. The BLOCKID of the Flash block,

where the data is stored, must be determined and stored at

SRAM address FAh.

The SRAM address of the first of the 64 bytes to be stored in

Flash must be indicated using the POINTER variable in the

parameter block (SRAM address FBh). Finally, the CLOCK and

DELAY value must be set correctly. The CLOCK value deter-

mines the length of the write pulse that is used to store the data

in the Flash. The CLOCK and DELAY values are dependent on

the CPU speed and must be set correctly.

9.5.4 EraseBlock Function

The EraseBlock function is used to erase a block of 64

contiguous bytes in Flash. The EraseBlock function first checks

the protection bits and determines if the desired BLOCKID is

writable. If write protection is turned on, the EraseBlock function

exits setting the accumulator and KEY2 back to 00h. KEY1 has

a value of 01h, indicating a write failure. The EraseBlock function

is only useful as the first step in programming. When a block is

erased, the data in the block is not one hundred percent

unreadable. If the objective is to obliterate data in a block, the

best method is to perform an EraseBlock followed by a Write-

Block of all zeros.

To set up the parameter block for the EraseBlock function,

correct key values must be stored in KEY1 and KEY2. The block

number to be erased must be stored in the BLOCKID variable

and the CLOCK and DELAY values must be set based on the

current CPU speed.

9.5.5 ProtectBlock Function

The enCoRe II devices offer Flash protection on a block by block

basis.

lists the protection modes available. In this table,

ER and EW indicate the ability to perform external reads and

writes. For internal writes, IW is used. Internal reading is

permitted by way of the ROMX instruction. The ability to read by

way of the SROM ReadBlock function is indicated by SR. The

protection level is stored in two bits according to

These bits are bit packed into the 64 bytes of the protection

block. As a result, each protection block byte stores the

protection level for four Flash blocks. The bits are packed into a

byte, with the lowest numbered block’s protection level stored in

The first address of the protection block contains the protection

level for blocks 0 through 3; the second address is for blocks 4

through 7. The 64th byte stores the protection level for blocks

252 through 255.

The level of protection is only decreased by an EraseAll, which

places zeros in all locations of the protection block. To set the

level of protection, the ProtectBlock function is used. This

function takes data from SRAM, starting at address 80h, and

ORs it with the current values in the protection block. The result

of the OR operation is then stored in the protection block. The

EraseBlock function does not change the protection level for a

block. Because the SRAM location for the protection data is fixed

and there is only one protection block per Flash macro, the

ProtectBlock function expects very few variables in the

parameter block to be set before calling the function. The

parameter block values that must be set, besides the keys, are

the CLOCK and DELAY values.

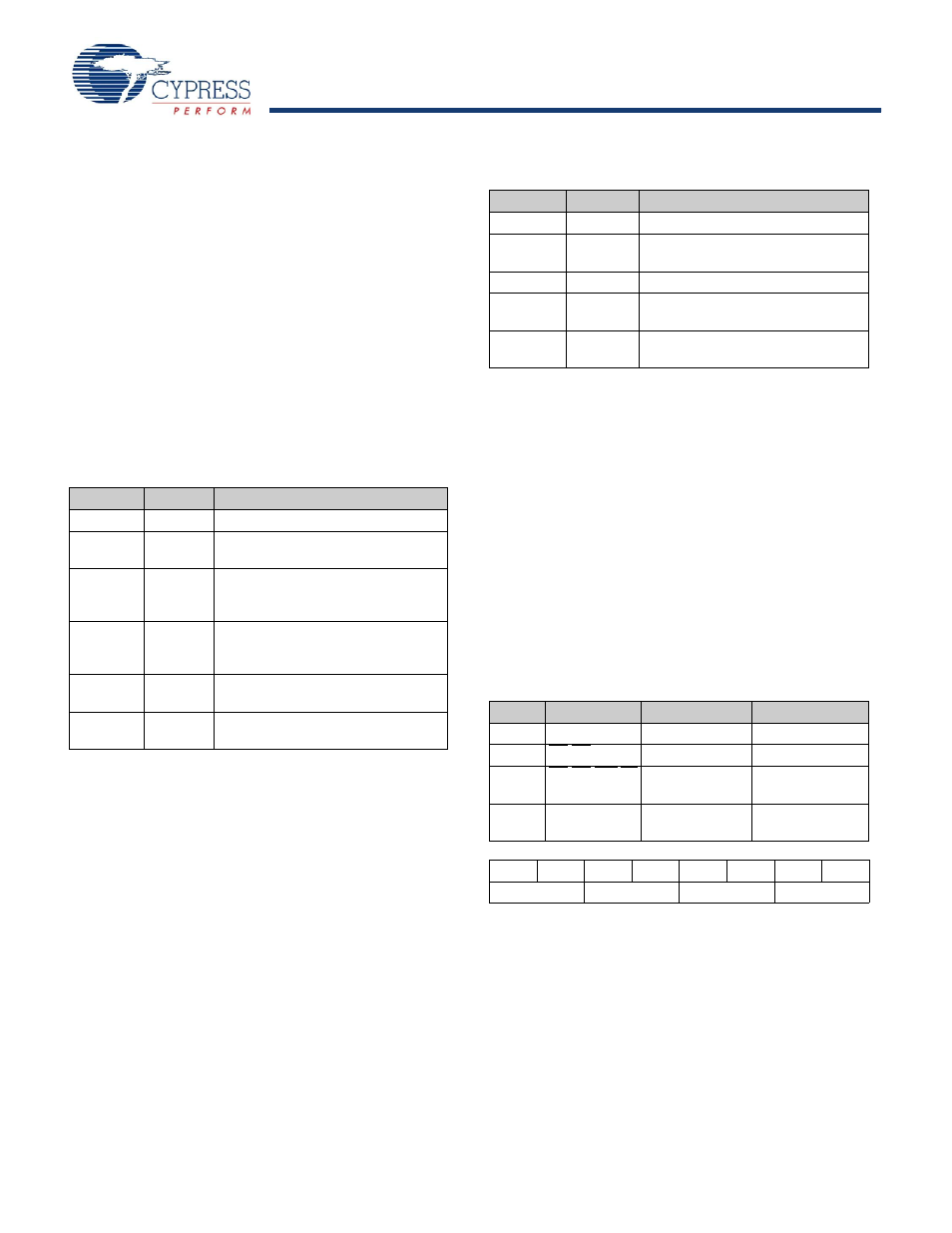

Table 9-5. WriteBlock Parameters

Name

Address

Description

KEY1

0,F8h

3Ah

KEY2

0,F9h

Stack Pointer value, when SSC is

executed.

BLOCKID

0,FAh

8KB Flash block number (00h–7Fh)

4KB Flash block number (00h–3Fh)

3KB Flash block number (00h–2Fh)

POINTER

0,FBh

First of 64 addresses in SRAM, where

the data to be stored in Flash is

located before calling WriteBlock.

CLOCK

0,FCh

Clock divider used to set the write

pulse width.

DELAY

0,FEh

For a CPU speed of 12 MHz set to

56h.

Table 9-6. EraseBlock Parameters

Name

Address

Description

KEY1

0,F8h

3Ah

KEY2

0,F9h

Stack Pointer value, when SSC is

executed.

BLOCKID

0,FAh

Flash block number (00h–7Fh)

CLOCK

0,FCh

Clock divider used to set the erase

pulse width.

DELAY

0,FEh

For a CPU speed of 12 MHz set to

56h

Table 9-7. Protection Modes

Mode

Settings

Description

Marketing

00b

SR ER EW IW Unprotected

Unprotected

01b

SR ER EW IW Read protect

Factory upgrade

10b

SR ER EW IW Disable external

write

Field upgrade

11b

SR ER EW IW Disable internal

write

Full protection

7

6

5

4

3

2

1

0

Block n+3

Block n+2

Block n+1

Block n