8 checksum function, Clocking – Cypress enCoRe CY7C63310 User Manual

Page 19

CY7C63310, CY7C638xx

Document 38-08035 Rev. *K

Page 19 of 83

9.5.8 Checksum Function

The Checksum function calculates a 16-bit checksum over a

user specifiable number of blocks, within a single Flash macro

(Bank) starting from block zero. The BLOCKID parameter is

used to pass in the number of blocks to calculate the checksum

over. A BLOCKID value of 1 calculates the checksum of only

block 0, while a BLOCKID value of 0 calculates the checksum of

all 256 user blocks. The 16-bit checksum is returned in KEY1 and

KEY2. The parameter KEY1 holds the lower eight bits of the

checksum and the parameter KEY2 holds the upper eight bits of

the checksum.

The checksum algorithm executes the following sequence of

three instructions over the number of blocks times 64 to be

checksummed.

romx

add [KEY1], A

adc [KEY2], 0

10. Clocking

The enCoRe II has two internal oscillators, the Internal 24 MHz

Oscillator and the 32 kHz Low power Oscillator.

The Internal 24 MHz Oscillator is designed such that it may be

trimmed to an output frequency of 24 MHz over temperature and

voltage variation. With the presence of USB traffic, the Internal

24 MHz Oscillator may be set to precisely tune to the USB timing

requirements (24 MHz ± 1.5%). Without USB traffic, the Internal

24 MHz Oscillator accuracy is 24 MHz ± 5% (between 0°–70°C).

No external components are required to achieve this level of

accuracy.

The internal low speed oscillator of nominally 32 kHz provides a

slow clock source for the enCoRe II in suspend mode, particu-

larly to generate a periodic wakeup interrupt and also to provide

a clock to sequential logic during power up and power down

events when the main clock is stopped. In addition, this oscillator

can also be used as a clocking source for the Interval Timer clock

(ITMRCLK) and Capture Timer clock (TCAPCLK). The 32 kHz

Low power Oscillator can operate in low power mode or can

provide a more accurate clock in normal mode. The Internal

32 kHz Low power Oscillator accuracy ranges (between

0°–70° C) follow:

■

5V Normal mode: –8% to + 16%

■

5V LP mode: +12% to + 48%

When using the 32 kHz oscillator, the PITMRL/H registers must

be read until 2 consecutive readings match before the result is

considered valid. The following firmware example assumes the

developer is interested in the lower byte of the PIT.

Read_PIT_counter:

mov A, reg[PITMRL]

mov [57h], A

mov A, reg[PITMRL]

mov [58h], A

mov [59h], A

mov A, reg[PITMRL]

mov [60h], A

;;;Start comparison

mov A, [60h]

mov X, [59h]

sub A, [59h]

jz done

mov A, [59h]

mov X, [58h]

sub A, [58h]

jz done

mov X, [57h]

;;;correct data is in memory location 57h

done:

mov [57h], X

ret

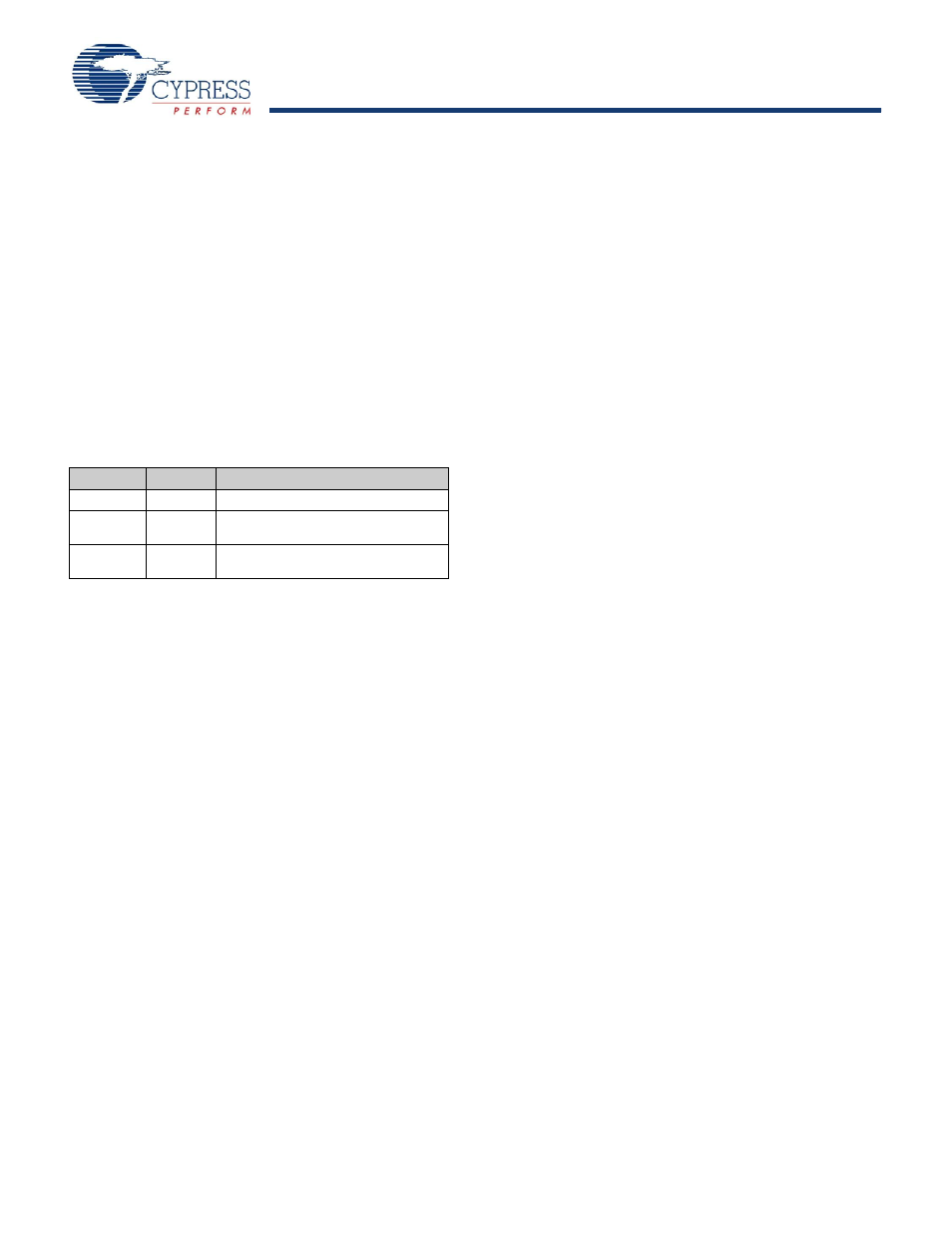

Table 9-12. Checksum Parameters

Name

Address

Description

KEY1

0,F8h

3Ah

KEY2

0,F9h

Stack Pointer value when SSC is

executed.

BLOCKID

0,FAh

Number of Flash blocks to calculate

checksum on.