Table 17-6 – Cypress enCoRe CY7C63310 User Manual

Page 53

CY7C63310, CY7C638xx

Document 38-08035 Rev. *K

Page 53 of 83

Table 17-5. Interrupt Mask 3 (INT_MSK3) [0xDE] [R/W]

Bit #

7

6

5

4

3

2

1

0

Field

ENSWINT

Reserved

Read/Write

R/W

–

–

–

–

–

–

–

Default

0

0

0

0

0

0

0

0

Bit 7:

Enable Software Interrupt (ENSWINT)

0= Disable. Writing 0s to an INT_CLRx register, when ENSWINT is cleared, causes the corresponding interrupt to clear

1= Enable. Writing 1s to an INT_CLRx register, when ENSWINT is set, causes the corresponding interrupt to post.

Bit [6:0]:

Reserved

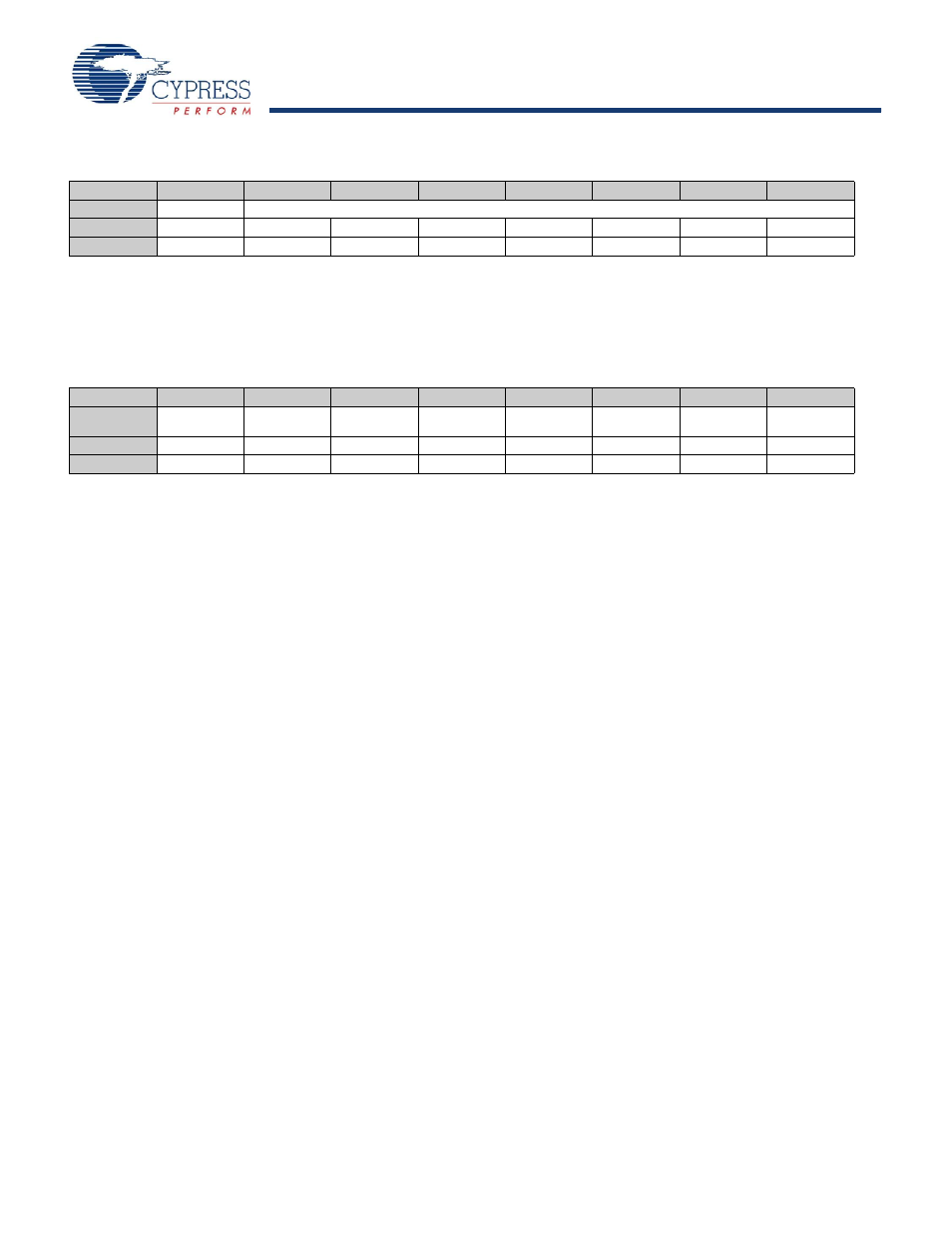

Table 17-6. Interrupt Mask 2 (INT_MSK2) [0xDF] [R/W]

Bit #

7

6

5

4

3

2

1

0

Field

Reserved

Reserved

GPIO Port 3

Int Enable

GPIO Port 2

Int Enable

PS/2 Data Low

Int Enable

INT2

Int Enable

16-bit Counter

Wrap Int Enable

TCAP1

Int Enable

Read/Write

–

R/W

R/W

R/W

R/W

R/W

R/W

R/W

Default

0

0

0

0

0

0

0

0

Bit 7:

Reserved

Bit 6:

GPIO Port 4 Interrupt Enable

0 = Mask GPIO Port 4 interrupt

1 = Unmask GPIO Port 4 interrupt

Bit 5:

GPIO Port 3 Interrupt Enable

0 = Mask GPIO Port 3 interrupt

1 = Unmask GPIO Port 3 interrupt

Bit 4:

GPIO Port 2 Interrupt Enable

0 = Mask GPIO Port 2 interrupt

1 = Unmask GPIO Port 2 interrupt

Bit 3:

PS/2 Data Low Interrupt Enable

0 = Mask PS/2 Data Low interrupt

1 = Unmask PS/2 Data Low interrupt

Bit 2:

INT2 Interrupt Enable

0 = Mask INT2 interrupt

1 = Unmask INT2 interrupt

Bit 1:

16-bit Counter Wrap Interrupt Enable

0 = Mask 16-bit Counter Wrap interrupt

1 = Unmask 16-bit Counter Wrap interrupt

Bit 0:

TCAP1 Interrupt Enable

0 = Mask TCAP1 interrupt

1 = Unmask TCAP1 interrupt