Rev. 1.0 35 – Maxim Integrated 73S12xxF User Manual

Page 35

UG_12xxF_018

Using Synchronous Smart Cards with the 73S12xxF

Rev. 1.0

35

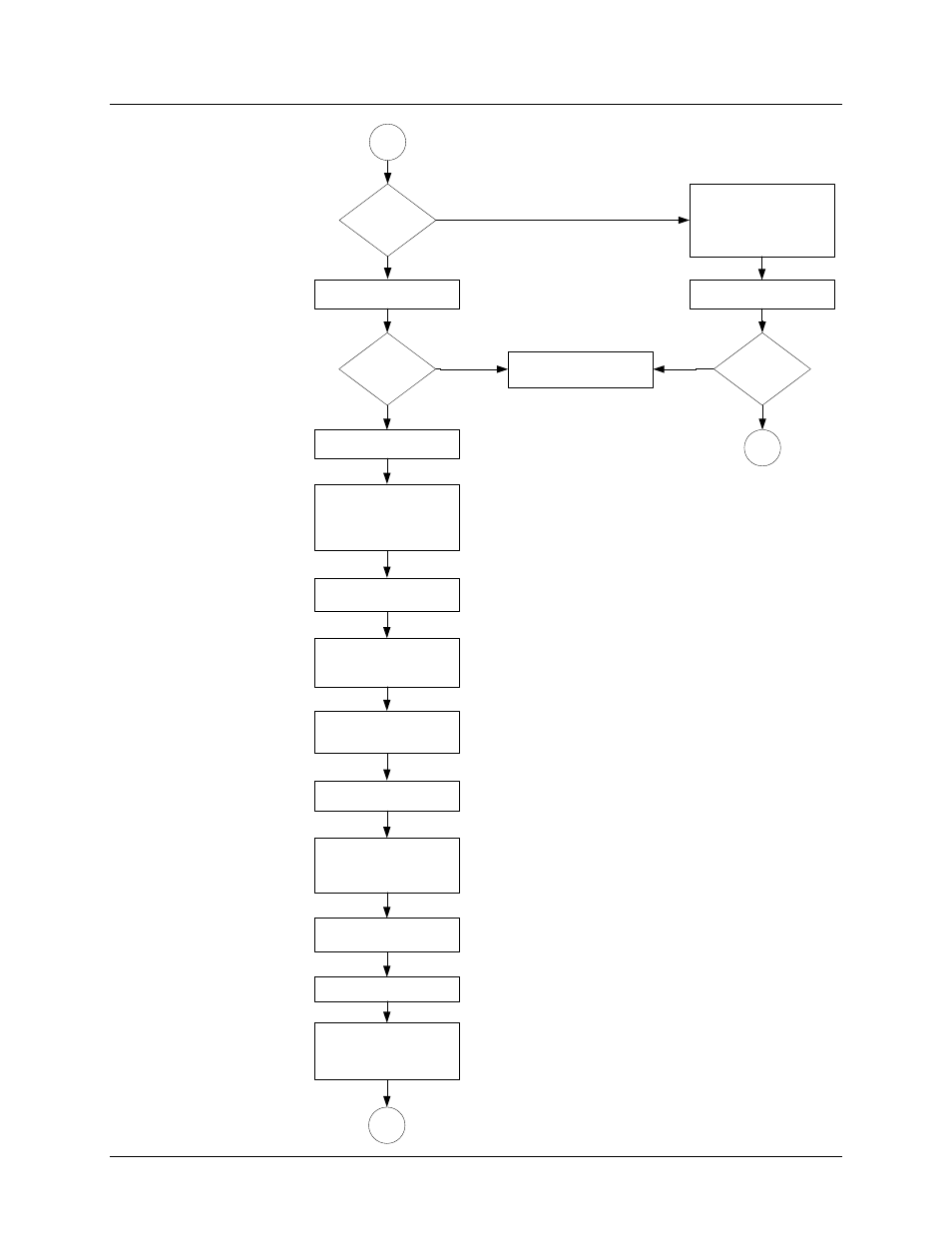

CLK is left running so ACK can fininsh and I/O

should be set high to prepare for stop bit. It

won't go low until the CLK is stopped.

Delay 1/2 ETU

ACK bit clear?

Yes

No

Process ACK error and try

again

Delay 1/2 ETU

ACK bit clear?

Yes

No

E

Stop CLK and set I/O for

output/high,

clear IOD and set CLKLVL

IO and CLKOFF bits

in SCCtl

Disable smart card

interrupts. SCIE = 0

Delay 1/2 ETU

Remaining bytes contain data

address high and low plus 1 to n

data bytes

Last data

byte sent?

No

Yes

Write next byte of data to

STXData and write 9 to

RLEN

D

Set IO for output/high to set up for start bit

Setup for I

2

C mode of operation and

reset bit counter

Set I

2

C and transmit mode.

Set SYCKST and TX/RXB

bits in STXCTL

Set I

2

C and receive mode.

Set SYCKST and clear

TX/RXB bit in STXCTL

Write device address byte to

STXDATA (read)

This is the I

2

C address, MSB data address bit and R/W

bit set for read

Keep CLK off and set I/O

for output/low,

clear IOD and IO bits and

set CLKOFF in SCCtl

Start bit

Allow at least 1 full ETU for the last ACK to clear before

generating start bit

Delay 1 ETU

Write 9 to RLEN

Keep I/O at output/low and

start CLK,

clear IO, IOD and

CLKOFF bits in SCCtl

Start CLK.

F