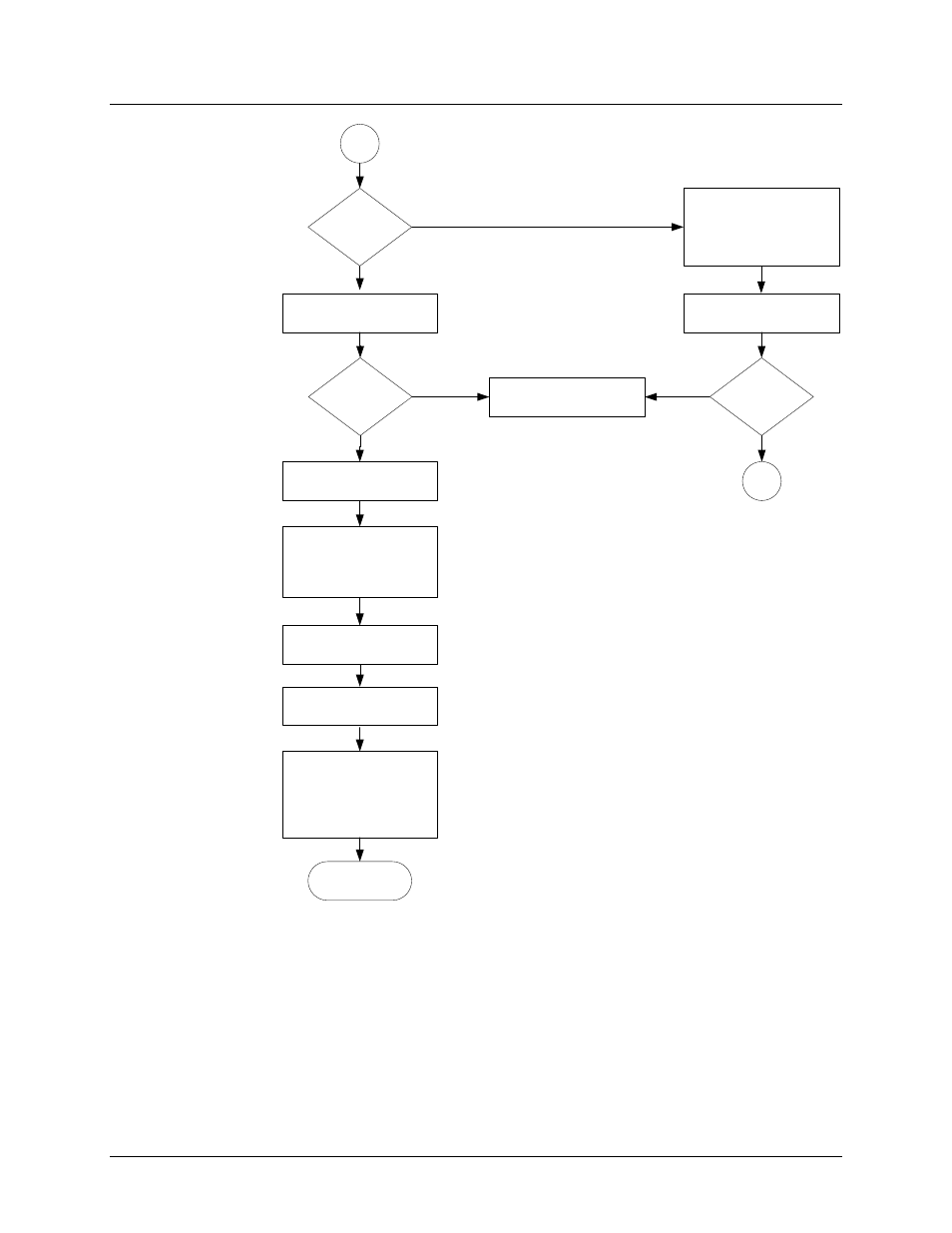

Figure 31: i, C write data flowchart, Figure 31 – Maxim Integrated 73S12xxF User Manual

Page 33

UG_12xxF_018

Using Synchronous Smart Cards with the 73S12xxF

Rev. 1.0

33

CLK is left running so ACK can fininsh and I/O

should be set high to prepare for stop bit. It

won't go low until the CLK is stopped.

Delay 1/2 ETU

ACK bit clear?

Yes

No

Process ACK error and try

again

Delay 1/2 ETU

ACK bit clear?

Yes

No

C

Allow 1 full ETU for the last ACK to clear before generating stop bit.

Stop CLK high and set I/O

for output/low,

clear IOD, IO and set

CLKLVL and CLKOFF bits

in SCCtl

Disable smart card

interrupts. SCIE = 0

END

Delay 1 ETU

Leave CLK off high and set

I/O for output/high,

clear IOD bit and set

CLKOFF , CLKLVL and IO

bits in SCCtl

Stop CLK and generate stop bit.

It should be noted that the write operations require some time to

execute and therefore no further operations can be executed. Any

attempt to send a command to the card will return a NAK response

until this write time has been reached.

Delay 1/2 ETU

Remaining bytes contain data

address high and low plus 1 to n

data bytes

Last data

byte sent?

No

Yes

Write next byte of data to

STXData and write 9 to

RLEN

B

Set IO for output/low to set up for stop bit.

Figure 31: I

2

C Write Data Flowchart