5 oscillators/clocks – Digilent 410-274P-KIT User Manual

Page 8

Nexys4™ FPGA Board Reference Manual

Copyright Digilent, Inc. All rights reserved.

Other product and company names mentioned may be trademarks of their respective owners.

Page 8 of 29

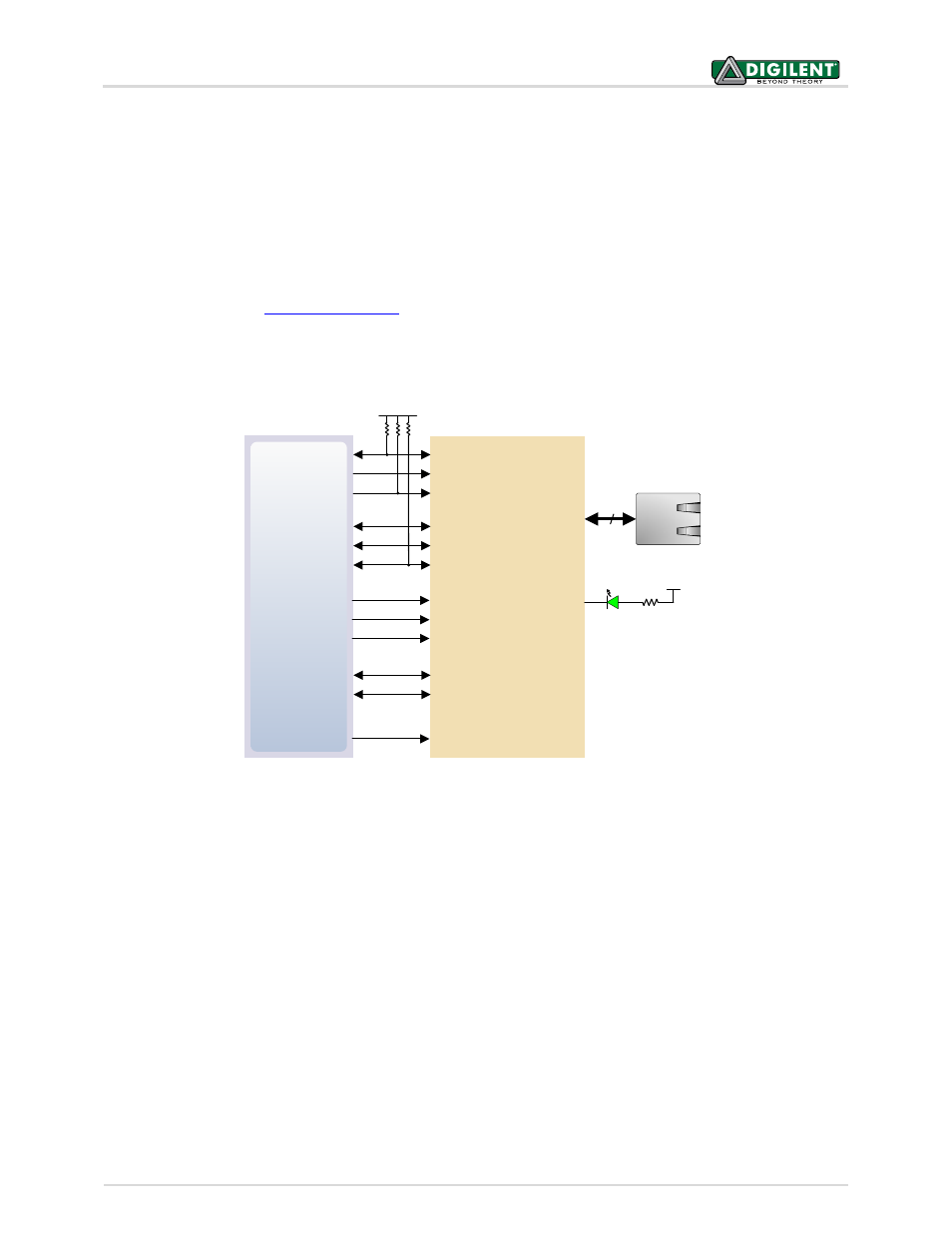

Two on-board LEDs (LD23 = LED2, LD24 = LED1) connected to the PHY provide link status and data activity

feedback. See the PHY datasheet for details.

EDK-based designs can access the PHY using either the axi_ethernetlite (AXI EthernetLite) IP core or the

axi_ethernet (Tri Mode Ethernet MAC) IP core. A mii_to_rmii core (Ethernet PHY MII to Reduced MII) needs to be

inserted to convert the MAC interface from MII to RMII. Also, a 50 MHz clock needs to be generated for the

mii_to_rmii core and the CLKIN pin of the external PHY. To account for skew introduced by the mii_to_rmii core,

generate each clock individually, with the external PHY clock having a 45 degree phase shift relative to the

mii_to_rmii Ref_Clk. An EDK demonstration project that properly uses the Ethernet PHY can be found on the

Nexys4 product page a

ISE designs can use the IP Core Generator wizard to create an Ethernet MAC controller IP core.

NOTE: Refer to the LAN8720A data sheet on the www.smsc.com website for further information.

D10

C9

A9

Artix-7

B3

RESET#

INT#/REFCLK0

CRS_DV/MODE2

TXEN

MDIO

4

MDC

C11

B8

D9

RXD1/MODE1

TXD0

SMSC LAN8720A

RJ-45 with

magnetics

Link/Status

LEDs (x2)

TXD1

RXD0/MODE0

RXERR/PHYAD0

CLKIN

D5

B9

A8

A10

C10

5 Oscillators/Clocks

The Nexys4 board includes a single 100MHz crystal oscillator connected to pin E3 (E3 is a MRCC input on bank 35).

The input clock can drive MMCMs or PLLs to generate clocks of various frequencies and with known phase

relationships that may be needed throughout a design. Some rules restrict which MMCMs and PLLs may be driven

by the 100MHz input clock. For a full description of these rules and of the capabilities of the Artix-7 clocking

resources, refer to the “7 Series FPGAs Clocking Resources User Guide” available from Xilinx.

Xilinx offers the Clocking Wizard IP core to help users generate the different clocks required for a specific design.

This wizard will properly instantiate the needed MMCMs and PLLs based on the desired frequencies and phase

relationships specified by the user. The wizard will then output an easy to use wrapper component around these

Figure 5. Pin connections between the Artix-7 and the Ethernet PHY