13 accelerometer, 1 spi interface, 2 interrupts – Digilent 410-274P-KIT User Manual

Page 24

Nexys4™ FPGA Board Reference Manual

Copyright Digilent, Inc. All rights reserved.

Other product and company names mentioned may be trademarks of their respective owners.

Page 24 of 29

13 Accelerometer

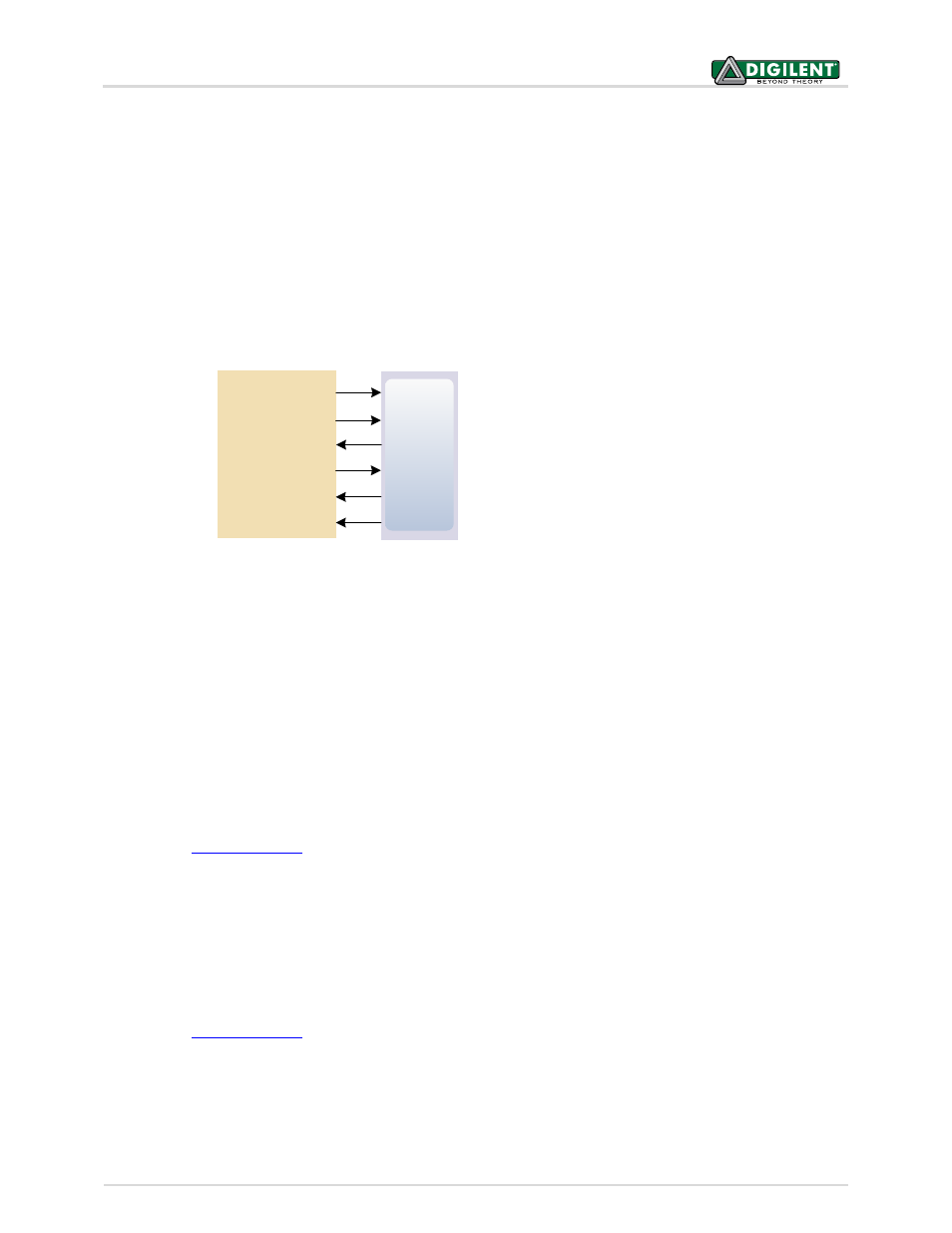

The Nexys4 includes an Analog Device ADXL362 accelerometer. The ADXL362 is a 3-axis MEMS accelerometer that

consumes less than 2 μA at a 100 Hz output data rate and 270 nA when in motion triggered wake-up mode. Unlike

accelerometers that use power duty cycling to achieve low power consumption, the ADXL362 does not alias input

signals by under-sampling; it samples the full bandwidth of the sensor at all data rates. The ADXL362 always

provides 12-bit output resolution; 8-bit formatted data is also provided for more efficient single-byte transfers

when a lower resolution is sufficient. Measurement ranges of ±2 g, ±4 g, and ±8 g are available, with a resolution of

1 mg/LSB on the ±2 g range. The FPGA can talk with the ADXL362 via SPI interface. While the ADXL362 is in

Measurement Mode, it continuously measures and stores acceleration data in the X-data, Y-data, and Z-data

registers. The interface between the FPGA and accelerometer can be seen in Fi 23.

Artix 7

ADXL362

MISO

~CS

SCLK

D13

C15

D15

MOSI: Master Out Slave In

MISO: Master In Slave Out

~CS: Slave Select (Active Low)

B14

MOSI

SCLK: Serial Clock

INT2

INT1

E15

C16

INT1: Interrupt One

INT2: Interrupt Two

13.1 SPI Interface

The ADXL362 acts as a slave device using an SPI communication scheme. The recommended SPI clock frequency

ranges from 1MHz to 5MHz. The SPI interface operates in SPI mode 0 with CPOL = 0 and CPHA = 0. All

communications with the device must specify a register address and a flag that indicate whether the

communication is a read or a write. Actual data transfer always follows the register address and communication

flag. Device configuration can be performed by writing to the control registers within the accelerometer. Access

accelerometer data by reading the device registers.

For a full list of registers, their functionality, and communication specifications, see the ADXL362 datasheet

available at:

13.2 Interrupts

Several of the built-in functions of the ADXL362 can trigger interrupts that alert the host processor of certain status

conditions. Interrupts can be mapped to either (or both) of two interrupt pins (INT1, INT2). Both of these pins

require internal FPGA pull-ups when used. For more details about the interrupts, see the ADXL362 datasheet

available at:

Figure 23. Accelerometer interface