4 ethernet phy, Artix-7 – Digilent 410-274P-KIT User Manual

Page 7

Nexys4™ FPGA Board Reference Manual

Copyright Digilent, Inc. All rights reserved.

Other product and company names mentioned may be trademarks of their respective owners.

Page 7 of 29

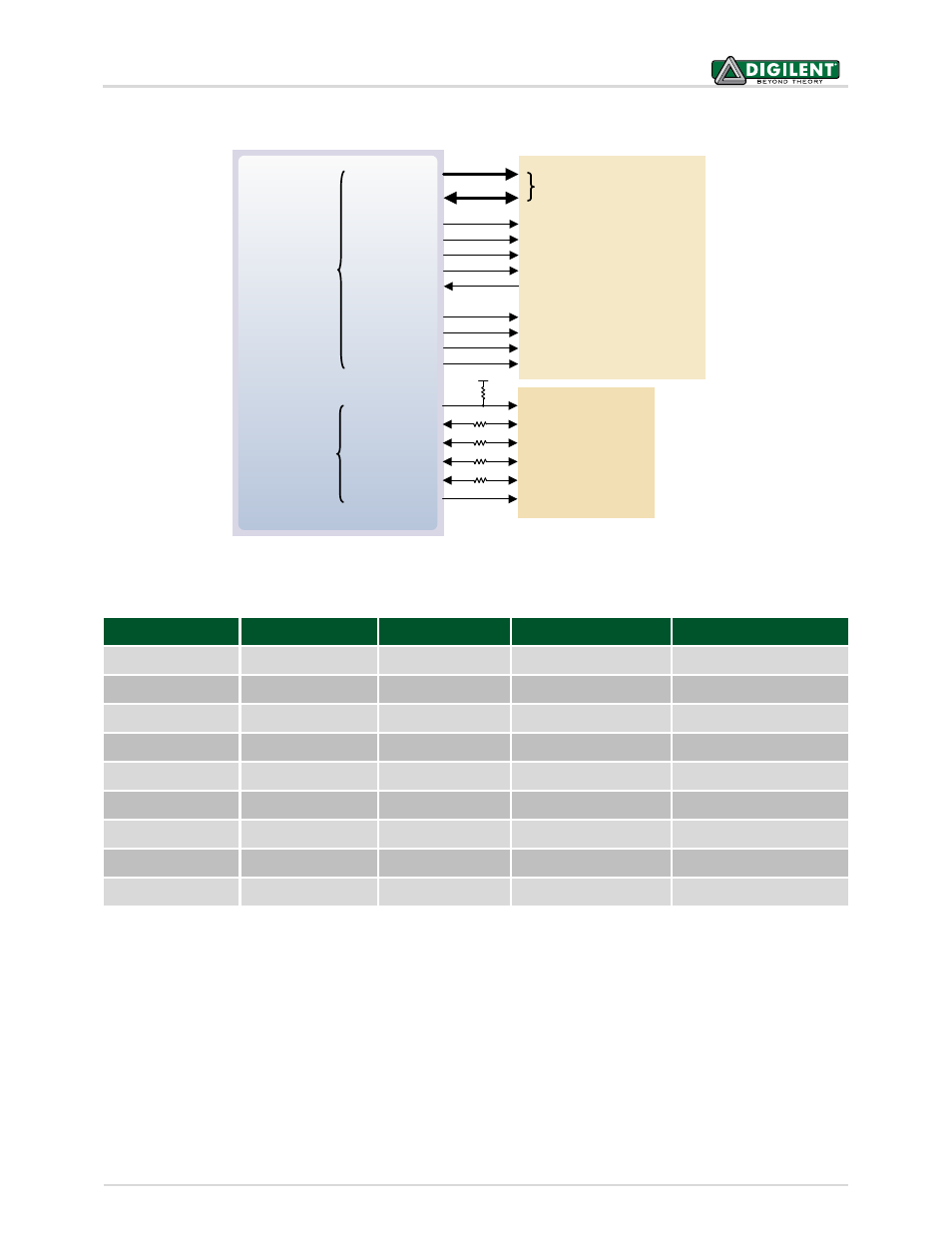

ADDR(22:0)

DATA(15:0)

Cellular RAM

CellRAM

CRE

LB#

UB#

CE#

WE#

OE#

CLK

WAIT

ADV#

CS#

SDI/DQ0

SDO/DQ1

E9

K18

K17

L13

SPI Flash

WP#/DQ2

HLD#/DQ3

L14

M14

SCK

Artix-7

H14

R11

T15

T13

T14

L18

J13

J15

J14

See Table

SPI Flash

4 Ethernet PHY

The Nexys4 board includes an SMSC 10/100 Ethernet PHY (SMSC part number LAN8720A) paired with an RJ-45

Ethernet jack with integrated magnetics. The SMSC PHY uses the RMII interface and supports 10/100 Mb/s. Figure

5 illustrates the pin connections between the Artix-7 and the Ethernet PHY. At power-on reset, the PHY is set to

the following defaults:

RMII mode interface

Auto-negotiation enabled, advertising all 10/100 mode capable

PHY address=00001

Figure 4. Nexys4 External Memories

Address Bus

Data Bus

ADDR22: U13

ADDR13: U16

ADDR4: H16

DATA15: P17

DATA6: T18

ADDR21: M16

ADDR12: P14

ADDR3: J17

DATA14: N17

DATA5: R17

ADDR20: T10

ADDR11: V12

ADDR2: H15

DATA13: P18

DATA4: U18

ADDR19: U17

ADDR10: V14

ADDR1: H17

DATA12: M17

DATA3: R13

ADDR18: V17

ADDR9: U14

ADDR0: J18

DATA11: M18

DATA2: U12

ADDR17: M13

ADDR8: V16

DATA10: G17

DATA1: T11

ADDR16: N16

ADDR7: N15

DATA9: G18

DATA0: R12

ADDR15: N14

ADDR6: K13

DATA8: F18

ADDR14: R15

ADDR5: K15

DATA7: R18

Table 3. CellRAM Address and Data Bus Pin Assignments