Master state machine, Figure 11: sbus master state machine – Achronix Speedster22i sBus User Manual

Page 21

UG047, October 24, 2013

21

Signal

Direction

Description

interface (from slave)

o_sbus_data[1:0]

Output

Output serial data of sBus

interface (to slave)

i_sbus_ack

Input

Acknowledgement signal for

read and write operation

complete on sBus interface

o_reg_rdwr_valid

Output

Read write operation

complete indication for

parallel interface

o_reg_rd_data[Pbus_Data_Width-1:0]

Output

Parallel Read data

i_reg_wr_data[Pbus_Data_Width-1:0]

Input

Parallel Write data

i_sw_rst

Input

Software reset when ack not

received

i_reg_address[16:0]

Input

Reg rd/wr address

i_reg_write

Input

Write operation on parallel

interface

i_reg_rw_req

Input

Read operation on parallel

interface

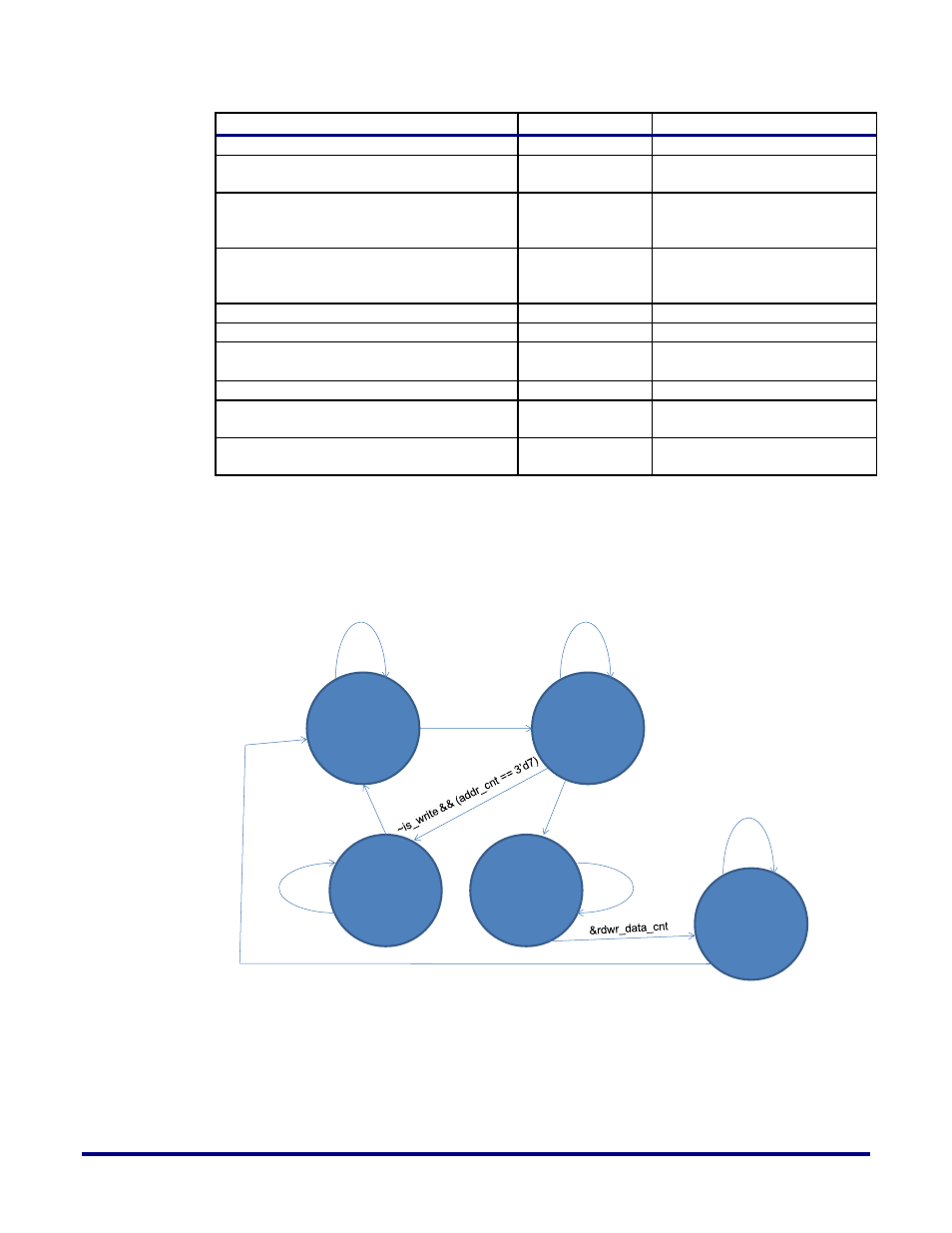

Master State Machine

Figure 11 shows the state machine for the sBus master implementation for the above

example.

ST_SBUS_IDLE

ST_SBUS_ADDR

ST_SBUS_WR_DATA

ST_SBUS_RD_DATA

ST_SBUS_WR

start_sbus_transfer

&rdwr_data_cnt

is_write && (addr_cnt

== 3’d7)

i_sbus_ack

~i_sbus_ack

addr_cnt

!= 3’d7

~start_sbus_transfer

~&rdwr_data_cnt

~&rdwr_data_cnt

Figure 11: sBus Master State Machine