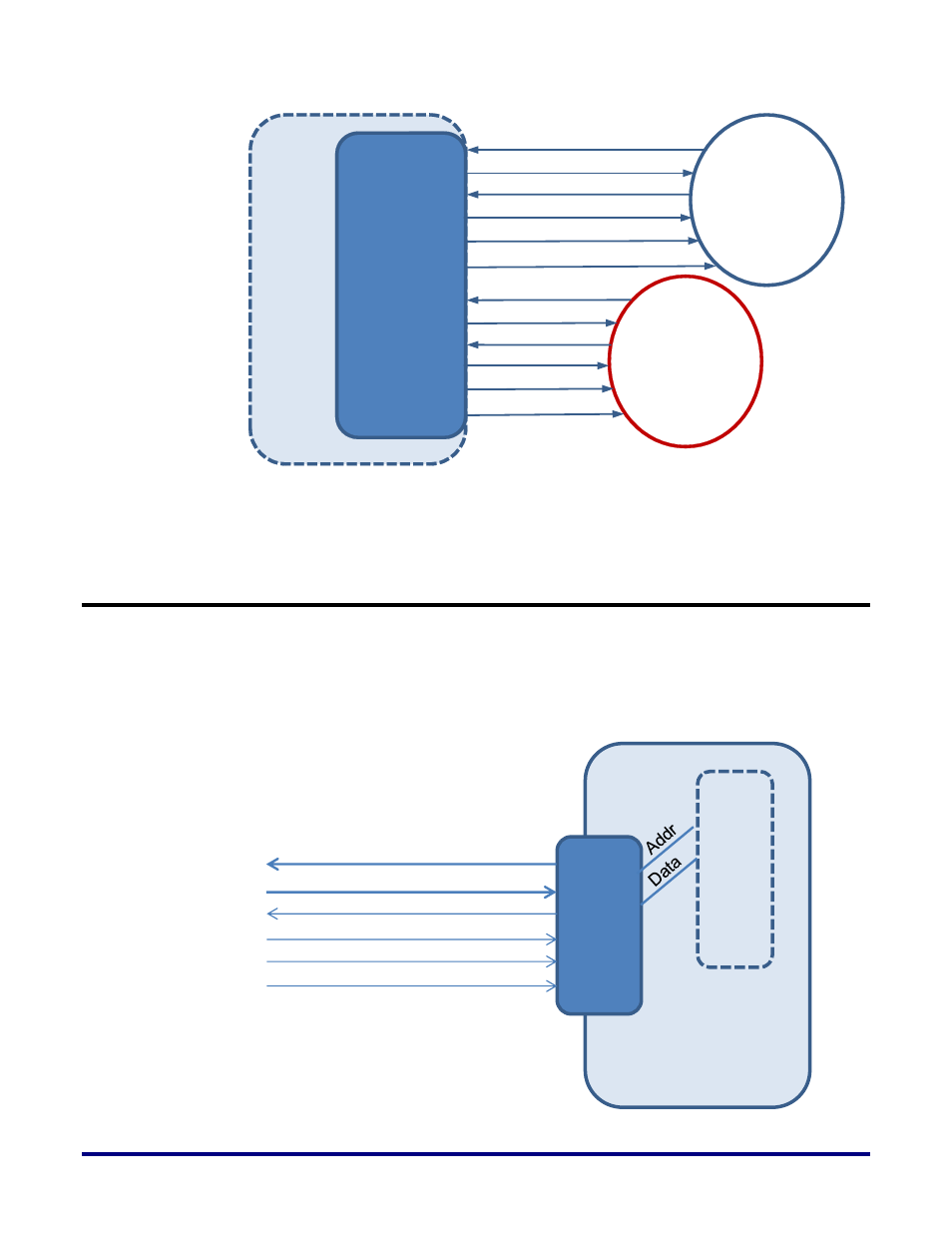

Slave interface, Figure 8: single master for two sbus slaves, Figure 9: sbus slave interface – Achronix Speedster22i sBus User Manual

Page 16: Slave, Figure 8, Hard ip sbus port, Fabric sbus port control logic, Slave 1 slave 2, Re g is te rs

16

UG047, October 24, 2013

Fabric

sBus Port

Control

Logic

sbus_clk

reset_sbus_clk

i_sbus_req

i_sbus_data [1:0]

o_sbus_ack

o_sbus_data [1:0]

Slave 1

Slave 2

Figure 8: Single Master for two sBus Slaves

Note: Achronix provides design examples for some of these implementations. Contact Achronix for

more information and help with your specific needs.

Slave Interface

The sBus slave interface typically has an 8-pin port as shown in Figure 9. For IPs that use

multiple lanes, for example, PCIe, the slave interface has the appropriate number of such

signal sets, and you must design the master accordingly. Refer to the Speedster22i PCIe User

Guide (UG030) for more details on the PCIe implementation.

Figure 9: sBus Slave Interface

Hard IP

sBus

Port

sbus_clk

reset_sbus_clk

i_sbus_req

i_sbus_data[1:0]

o_sbus_ack

o_sbus_data[1:0]

R

e

g

is

te

rs