Chapter 3, Sbus interfaces, Master interface – Achronix Speedster22i sBus User Manual

Page 15: Figure 7: single master for a single sbus slave, Master, Chapter 3 – sbus interfaces, Fabric sbus port control logic

UG047, October 24, 2013

15

Chapter 3

– sBus Interfaces

In this chapter, you will learn the following about the sBus serial bus:

Master Interface

You have the flexibility to design the sBus master depending on your needs. You could, for

example, do the following.

Design one master to address only one slave

Design one master to address multiple slaves

Design one master to accept data from multiple sources and direct it to one slave

Or design such combinations of each or any of the above

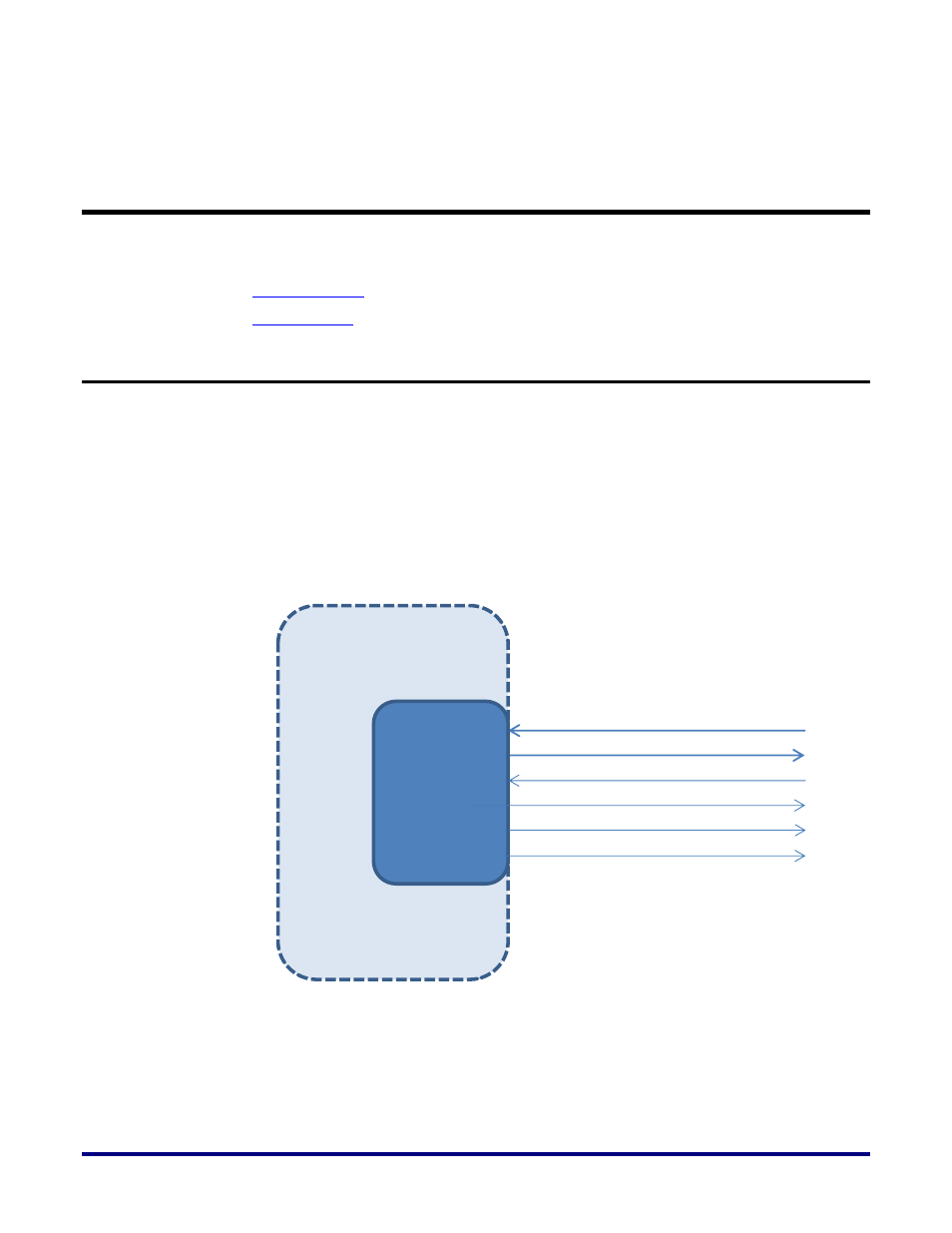

Figure 7 shows a single master generating and accepting the required signals for writes and

reads to the slave interface.

Fabric

sBus Port

Control

Logic

sbus_clk

reset_sbus_clk

i_sbus_req

i_sbus_data[1:0]

o_sbus_ack

o_sbus_data[1:0]

Figure 7: Single Master for a single sBus Slave

Figure 8 shows a single master generating and accepting the required signals for writes and

reads to two slave interfaces.