Chapter 2, Sbus functional description, Port list – Achronix Speedster22i sBus User Manual

Page 11: Read operation, Bit data-width mode, Table 1: hd1000 sbus port definition, Chapter 2 – sbus functional description

UG047, October 24, 2013

11

Chapter 2

– sBus Functional Description

In this chapter, you will learn the following about the sBus serial bus:

Port List

The sBus interface or port uses eight signals for operation. Table 1 lists these signals and their

functions. These signals can be driven directly by a state machine in the FPGA fabric. You can

find more information about designs based on these topologies in

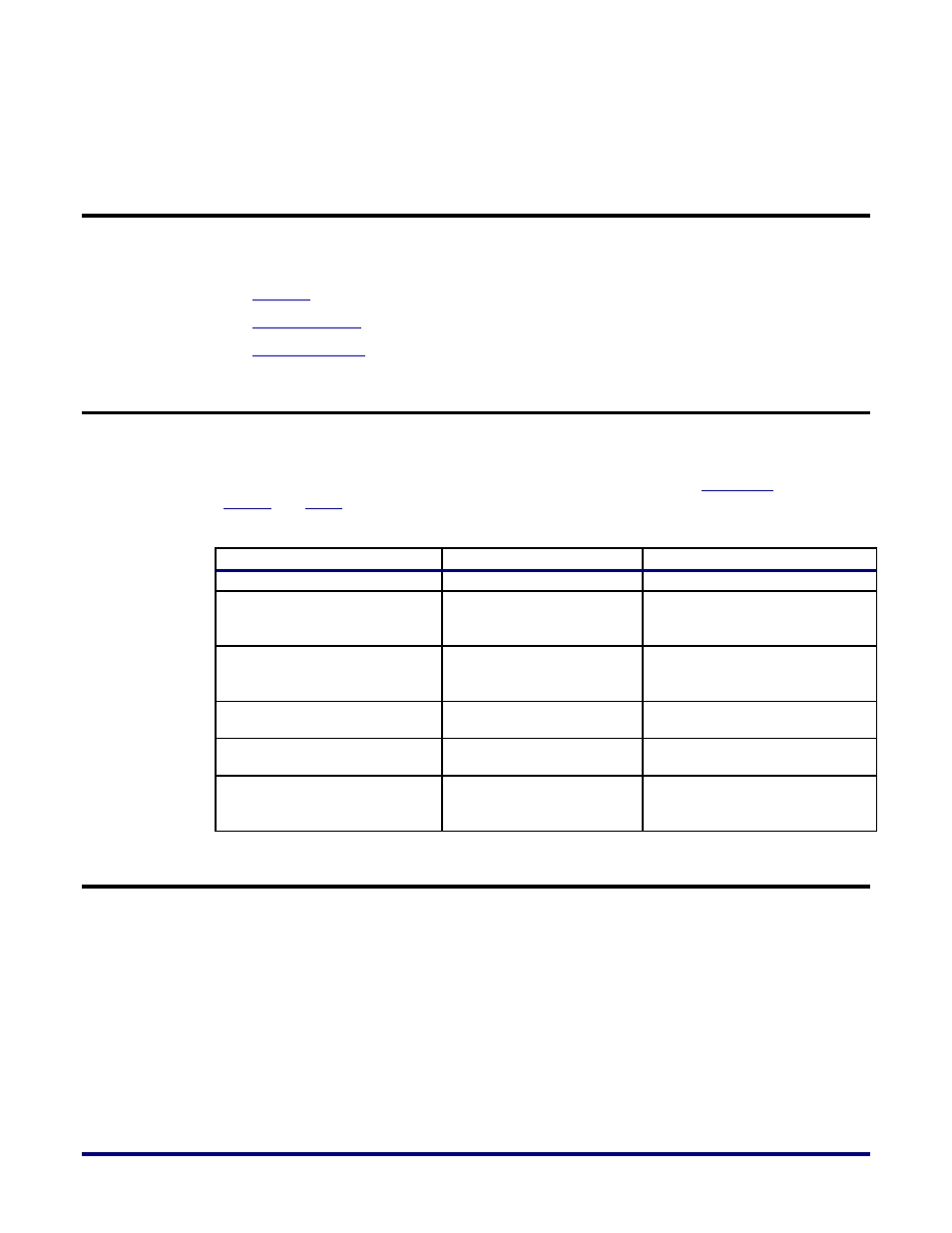

Table 1: HD1000 sBus Port Definition

Port

Direction

Description

reset_sbus_clk

Input

Asynchronous reset

sbus_clk

Input

Reference clock for the serial

and parallel interfaces

–

p1_ctl_clk

i_sbus_req

Input

Request signal for starting a

read or write transaction on

sBus.

i_sbus_data[1:0]

Input

Input serial data of sBus

interface.

o_sbus_data[1:0]

Output

Output serial data of sBus

interface.

o_sbus_ack

Output

Acknowledgement signal for

read and write operation

complete on sBus interface.

Read Operation

32-bit Data-width Mode

For a 32-bit data-width mode read operation, you must do the following.

1. Assert the i_sbus_req signal for 9 cycles.

2. De-assert i_sbus_data[0] during the first cycle.

3. Send the LSB of the 17-bit long read address on i_sbus_data[1] during the first cycle.

4. Send the remaining 16 bits of the read address on i_sbus_data[1:0] in the following order

[A2:A1]…[A16:A15] over the next 8 cycles.

5. De-assert i_sbus_req signal.

The sBus slave will decode the read operation and respond as follows.