Interfaces, Internal (core) interface – Achronix Speedster22i DDR User Manual

Page 9

Interfaces

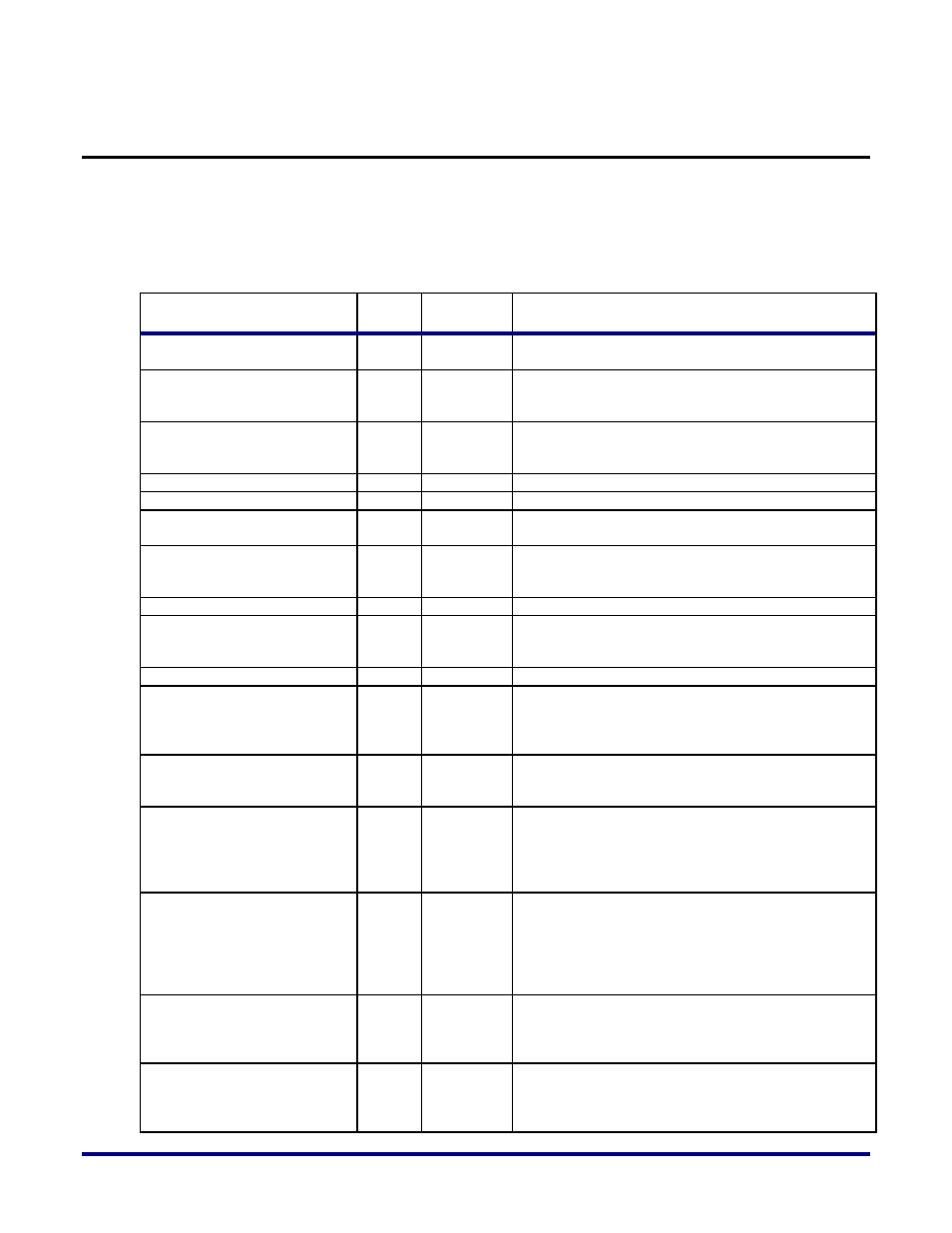

Internal (core) Interface

The internal interface to the PHY/DDR controller, which is implemented in the core fabric, contains the

following interface signals as listed below in table 1.

Signal Name

Bus

Width

Direction

Description

clk

1

Input

Driven by user. Clock signal. This is the reference clock

coming in from the board.

ddr_int_clk_div2

1

Output

In 2X Clock mode the clock from PHY will be at half the

controller clock which should be used to send and receive data

from core to controller

ddr_int_clk_div4

1

Output

When the wide bus interface is enabled, the clock from PHY

will be at one quarter the controller clock which should be

used to send and receive data from core to controller

reset_ddr_phy_n

1

Input

Driven by user. Reset to PHY. Asserted active low.

reset_ddr_ctrlr_n

1

Input

Driven by user. Reset to DDR controller. Asserted active low.

ddr_int_busy

1

Output

Indicates that the DDR3 Controller is busy and is not accepting

new requests.

ddr_int_busy_align

1

Output

When the wide bus interface is enabled and in 2X clock mode,

indicates that the DDR3 Controller is busy and is not accepting

new requests.

ddr_int_addr

34

Input

Address bus containing row, column, and bank information.

ddr_int_burst_size

8

Input

Indicates burst size of given read/write request.

Valid ranges of this value are:

8’d4 8’d252 (multiples of 4) for DDR3

ddr_int_wr_request

1

Input

Write request.

ddr_int_wrdata_req

9

Output

Request by DDR Controller for data to be written to the DDR

Memory. This is asserted some number of clock cycles after a

write request, and is burst length number of clock cycles in

length per write request.

ddr_int_wrdata_req_early

9

Output

Early request by DDR controller for data to be written to the

DDR memory. Signal will be asserted earlier then

‘ddr_int_wrdata_req’ which can be used.

ddr_int_wrdata_req_align

9

Output

When the wide bus interface is enabled and in 2X Clock mode,

request by DDR Controller for data to be written to the DDR

Memory. This signal bus essentially performs a single

alignment function but is provided as a multi-bit signal for

timing purposes.

ddr_int_wrdata_req_early_align

9

Output

When the wide bus interface is enabled and in 2X Clock mode,

early request by DDR Controller for data to be written to the

DDR Memory. Signal will be asserted earlier then

‘ddr_int_wrdata_req_align’ which can be used. This signal bus

essentially performs a single alignment function but is

provided as a multi-bit signal for timing purposes.

ddr_int_wrdata

[SIZE*4-

1:0]

Input

Data to be written to the DDR Memory. This data is provided

two cycles after ddr_int_wrdata_req is asserted. SIZE: 72, 64,

32, 16, 8. When the wide bus interface is enabled, the SIZE

parameters and consequently the bus width, are doubled.

ddr_int_wrdata_mask

[SIZE/2-

1:0]

Input

Data mask corresponding to “ddr_int_wrdata”. When any

data mask bit is asserted, the data contained in the

corresponding ‘ddr_int_wrdata’ byte will not be written to

Memory. SIZE: 72, 64, 32, 16, 8. When the wide bus interface is

UG031, Nov 18, 2014

9