Overview – Achronix Speedster22i DDR User Manual

Page 5

Overview

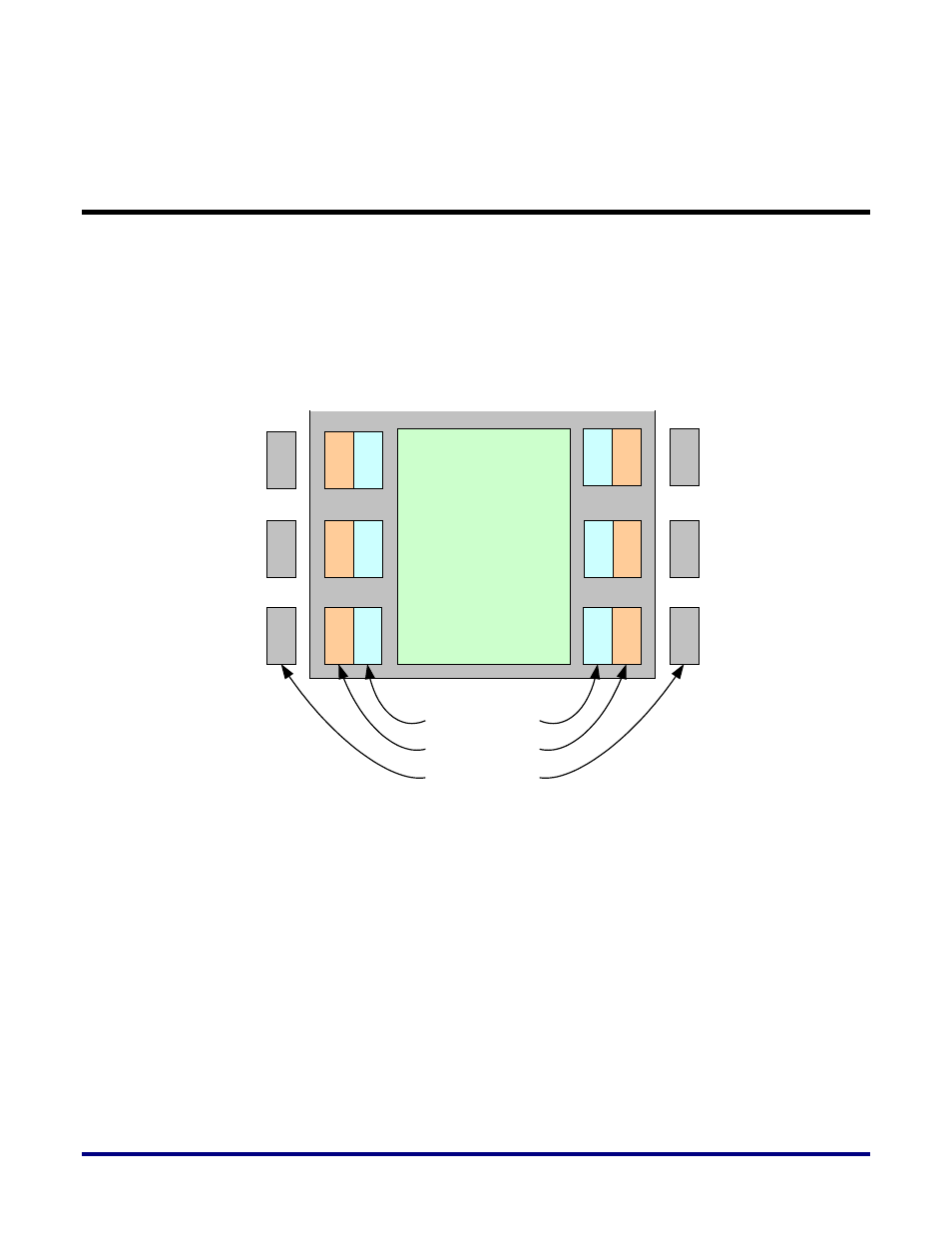

Achronix’s Speedster22i FPGAs contain up to six embedded DDR controllers which can be

used to interface with and control off-chip DDR2 or DDR3 memory devices, including

DIMMs. Each of the DDR controllers supports up to 72 bits of data and speeds of up to 1866

Mbps. The embedded DDR controllers and PHYs are implemented as Hard-IP blocks in the

frame of the Speedster22i FPGAs as illustrated in Figure 1 below.

Figure 1: Location of Speedster22i DDR Controllers and PHYs

Speedster22i DDR controllers support both “auto” and “custom” modes. Under the “auto”

mode functions such as (but not limited to) activating/precharging banks/rows, calibration

algorithms, and initialization sequences are handled by the embedded DDR Controller and

are transparent to the user. The mapping of byte-lanes to pins is also handled transparently

as the IOs are included in embedded DDR PHY Macro.

Under “custom” mode the user has the option to manually override functions such as

automated refresh and initialization engines/sequences.

Speedster22i FPGA

DDR PHY

DDR Controller

DDR Memory

(off-chip)

Speedster22i Core

WN

WS

EN

ES

EC

WC

UG031, Nov 18, 2014

5