Achronix Speedster22i DDR User Manual

Page 12

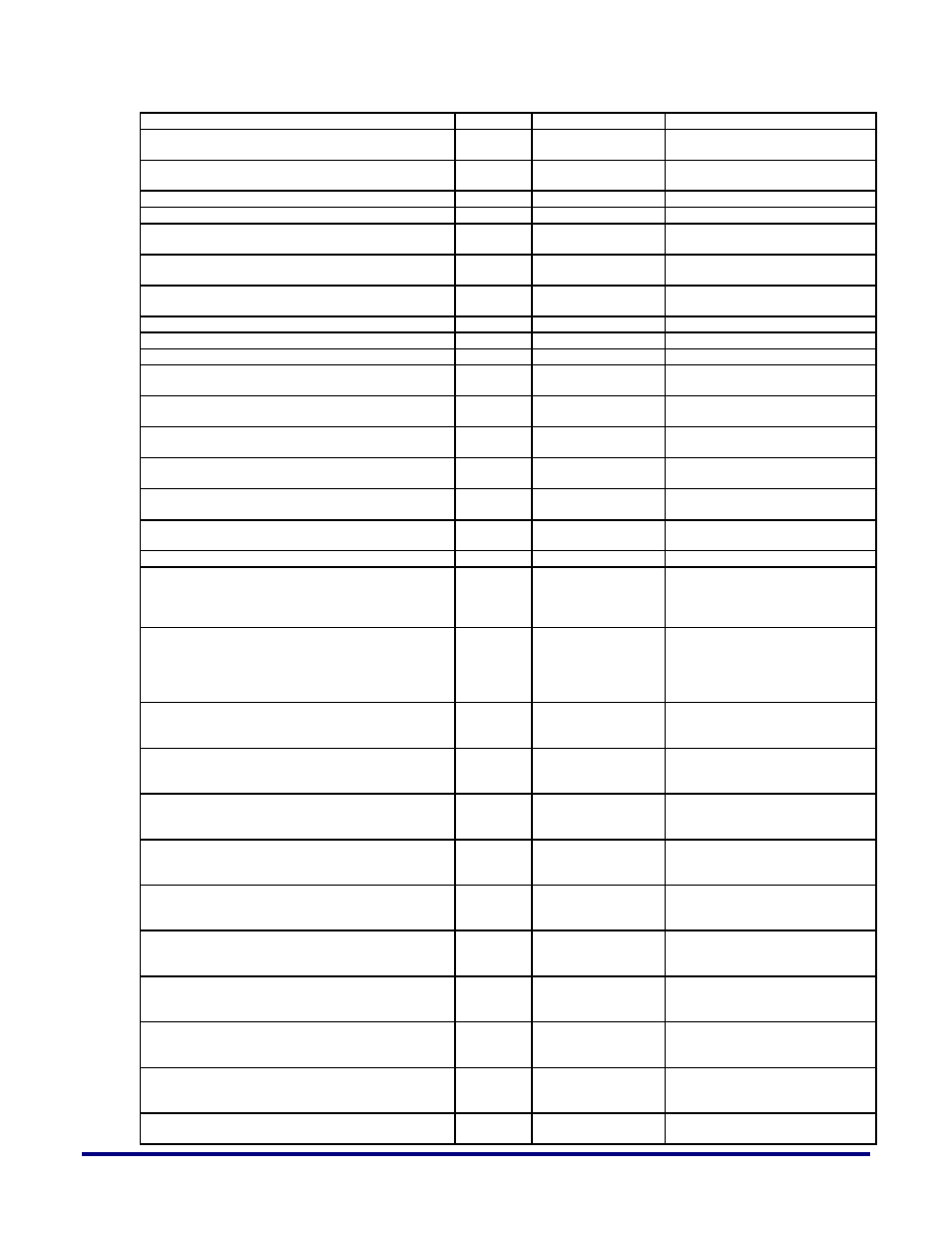

bank

DELAY_READ_TO_PRECHARGE

3'h4

4-6 clock cycles

Minimum Read to precharge (DDR3

only)

DELAY_WRITE_TO_PRECHARGE

4'h8

5-12 clock cycles

Minimum time from write to

PRECHARGE

DELAY_WRITE_TO_READ

3'h4

2-6 clock cycles

Minimum time from write to read.

DELAY_READ_TO_WRITE

3'h3

1-7 clock cycles

Read to write delay (valid values: 1

DELAY_WRITE_TO_WRITE_DIFF_BANK

3'h2

0-7 clock cycles

Minimum delay from write to write

(different ranks)

DELAY_WRITE_TO_READ_DIFF_BANK

3'h1

0-7 clock cycles

Minimum delay from write to read

(different ranks)

DELAY_READ_TO_READ_DIFF_BANK

3'h2

1-7 clock cycles

Minimum delay from read to read

(different ranks)

DELAY_ADDITIVE_DDR3_LATENCY

3'h0

0-5 clock cycles

Additive latency value (DDR2)

CAS_LATENCY

4'h7

5-11

Cas latency

CAS_WRITE LATENCY

4'h6

5-8

Cas Write latency

DELAY_LOADMODE_TO_ACTIVATE

3’h6

clock cycles

Minimum LOADMODE to ACTIVATE

command

DELAY_LOADMODE_TO_ANY

4’hE

clock cycles

Minimum LOADMODE to ANY

command

DELAY_SELF_REFRESH_TO_NON_DLL_CMD

9'h040

clock cycles

Minimum time from self refresh to non-

DLL command

DELAY_SELF_REFRESH_TO_NON_READ_CMD

8'h87

clock cycles

Minimum time from self refresh to non-

read command

DELAY_RESET_HIGH_TO_CLK_HIGH

9'h040

clock cycles

Minimum delay from memory reset

high to cke hig

REFRESH_PERIOD

16'h07D0

10-65535 refresh time

interval / tCK

Refresh period. This is the number of

clock cycles between refresh commands.

DELAY_STARTUP

19'h000c8

10-524287 clock cycles

Initialization delay after reset

NUM_COLUMN_BITS

3'h5

5, 6, 7

Number of column bits

5: 10 column bits

6: 11 column bits

7: 12 column bits

NUM_ROW_BITS

3'h3

2, 3, 4, 5

Number of row bits

2: 13 row bits

3: 14 row bits

4: 15 row bits

5: 16 row bits

NUM_BANK_BITS

1'h1

0, 1

Number of bank bits

0: 2 bank bits

1: 3 bank bits

REGISTERED_DIMM

1'h0

0,1

Registered dimm support

0: UDimm

1: RDimm

ODT_READ_CS0

8'h00

Each bank contains 8

bits, one per DQ. ODT

is enabled when set to 1

On die termination selection for reads

on cs0

ODT_READ_CS1

8'h00

Each bank contains 8

bits, one per DQ. ODT

is enabled when set to 1

On die termination selection for reads

on cs1

ODT_READ_CS2

8'h00

Each bank contains 8

bits, one per DQ. ODT

is enabled when set to 1

On die termination selection for reads

on cs2

ODT_READ_CS3

8'h00

Each bank contains 8

bits, one per DQ. ODT

is enabled when set to 1

On die termination selection for reads

on cs3

ODT_READ_CS4

8’h00

Each bank contains 8

bits, one per DQ. ODT

is enabled when set to 1

On die termination selection for reads

on cs4

ODT_READ_CS5

8’h00

Each bank contains 8

bits, one per DQ. ODT

is enabled when set to 1

On die termination selection for reads

on cs5

ODT_READ_CS6

8’h00

Each bank contains 8

bits, one per DQ. ODT

is enabled when set to 1

On die termination selection for reads

on cs6

ODT_READ_CS7

8’h00

Each bank contains 8

bits, one per DQ. ODT

On die termination selection for reads

on cs7

12

UG031, Nov 18, 2014